# Embedded Network Firewall on FPGA

A Thesis Submitted to the College of

Graduate Studies and Research

In Partial Fulfillment of the Requirements

For the degree of Master of Science

In the Department of Electrical and Computer Engineering

University of Saskatchewan

Saskatoon, Saskatchewan

Canada

By

Raouf Ajami

©Copyright Raouf Ajami, November, 2010. All rights reserved.

# PERMISSION TO USE

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Head of the Department of Electrical and Computer Engineering

57 Campus Drive

University of Saskatchewan

Saskatoon, Saskatchewan

Canada

S7N 5C9

# Abstract

The Internet has profoundly changed today's human being life. A variety of information and online services are offered by various companies and organizations via the Internet. Although these services have substantially improved the quality of life, at the same time they have brought new challenges and difficulties. The information security can be easily tampered by many threats from attackers for different purposes. A catastrophe event can happen when a computer or a computer network is exposed to the Internet without any security protection and an attacker can compromise the computer or the network resources for destructive intention.

The security issues can be mitigated by setting up a firewall between the inside network and the outside world. A firewall is a software or hardware network device used to enforce the security policy to the inbound and outbound network traffic, either installed on a single host or a network gateway. A packet filtering firewall controls the header field in each network data packet based on its configuration and permits or denies the data passing thorough the network.

The objective of this thesis is to design a highly customizable hardware packet filtering firewall to be embedded on a network gateway. This firewall has the ability to process the data packets based on: source and destination TCP/UDP port number, source and destination IP address range, source MAC address and combination of source IP address and destination port number. It is capable of accepting configuration changes in real time. An Altera FPGA platform has been used for implementing and evaluating the network firewall.

# ACKNOWLEDGEMENTS

I would like to sincerely appreciate my supervisor Dr. Anh V. Dinh for his advice, support and patience throughout this thesis work.

A special thanks to my friend, Vivek Joshi, for his help, guidance and suggestions during the course of this thesis writing.

Finally, I would like to express gratitude to my lovely wife, Mahasti, for encouragement and help during my studies. Many thanks to my parents for their support in my education.

# Contents

| P€           | ermis                  | $\mathbf{s}$ sion $\mathbf{t}$ | o Use                        | i    |

|--------------|------------------------|--------------------------------|------------------------------|------|

| $\mathbf{A}$ | bstra                  | ct                             |                              | ii   |

| A            | cknov                  | wledge                         | ements                       | iii  |

| Co           | onter                  | $_{ m nts}$                    |                              | iv   |

| Li           | ${ m st}$ of           | Table                          | ${f s}$                      | vii  |

| Li           | st of                  | Figur                          | es                           | viii |

| Li           | $\operatorname{st}$ of | Abbre                          | eviations                    | x    |

| 1            | Intr                   | oduct                          | ion                          | 1    |

|              | 1.1                    | Motiv                          | ation                        | . 1  |

|              | 1.2                    | Resear                         | rch objective                | . 3  |

|              | 1.3                    | Thesis                         | s outline                    | . 4  |

| 2            | Bac                    | kgrou                          | $\operatorname{nd}$          | 5    |

|              | 2.1                    | Netwo                          | ork security                 | . 5  |

|              |                        | 2.1.1                          | Security model               | . 7  |

|              |                        | 2.1.2                          | Firewall and traffic control | . 7  |

|              | 2.2                    | Comp                           | uter networking              | . 9  |

|              |                        | 2.2.1                          | Transport layer              | . 12 |

|              |                        | 2.2.2                          | Internet layer               | . 16 |

|              | 2.3                    | Embe                           | dded systems                 | . 19 |

|              |                        | 2.3.1                          | Altera design solution       | . 21 |

| 3            | $\mathbf{Eml}$         | bedde                          | d Network Firewall Design    | 27   |

|   | 3.1  | Hardw   | vare modules in the embedded network firewall            | 27 |

|---|------|---------|----------------------------------------------------------|----|

|   |      | 3.1.1   | Nios II microprocessor module                            | 29 |

|   |      | 3.1.2   | Ethernet module                                          | 32 |

|   |      | 3.1.3   | Content Associative Memory module                        | 34 |

|   |      | 3.1.4   | Network Firewall Module (NFM)                            | 37 |

|   |      | 3.1.5   | Network mask RAM module                                  | 41 |

|   |      | 3.1.6   | Arbiter module                                           | 43 |

|   |      | 3.1.7   | Status display module                                    | 43 |

|   | 3.2  | Softwa  | are modules in the embedded network firewall             | 46 |

|   |      | 3.2.1   | $\operatorname{MicroC/OS-II}$ real-time operating system | 47 |

|   |      | 3.2.2   | NicheStack TCP/IP Stack                                  | 48 |

|   |      | 3.2.3   | LAN91C111 device driver                                  | 48 |

|   |      | 3.2.4   | Initialization                                           | 49 |

|   |      | 3.2.5   | Telnet Server                                            | 52 |

|   |      | 3.2.6   | Configuration on the fly                                 | 53 |

|   |      | 3.2.7   | Monitoring                                               | 54 |

| 4 | Test | ting ar | nd Results                                               | 58 |

|   | 4.1  | Test to | pols                                                     | 58 |

|   |      | 4.1.1   | Wireshark                                                | 58 |

|   |      | 4.1.2   | Tcpdump                                                  | 59 |

|   |      | 4.1.3   | Ping                                                     | 59 |

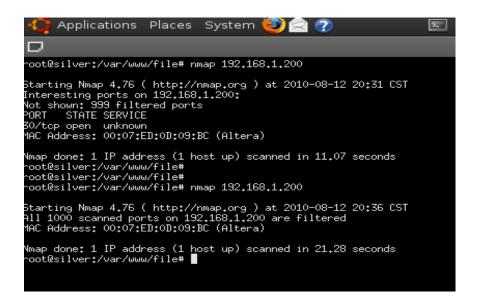

|   |      | 4.1.4   | Nmap                                                     | 59 |

|   | 4.2  | Testin  | g procedure                                              | 59 |

|   |      | 4.2.1   | Destination and source port mode                         | 61 |

|   |      | 4.2.2   | Source and destination IP address mode                   | 65 |

|   |      | 4.2.3   | Source IP address and destination port number mode       | 68 |

|   |      | 4.2.4   | Source MAC address mode                                  | 72 |

|   | 4.3  | Result  | S                                                        | 72 |

|   | 4.4  | Comp    | arisons                                                  | 77 |

| 5                | Sun   | nmary, Conclusions and Future works | 80 |

|------------------|-------|-------------------------------------|----|

|                  | 5.1   | Summary                             | 80 |

|                  | 5.2   | Conclusions                         | 82 |

|                  | 5.3   | Future works                        | 83 |

| $\mathbf{R}_{0}$ | efere | nces                                | 85 |

# LIST OF TABLES

| 1.1 | Estimation of malware financial impact [1]                              | 2  |

|-----|-------------------------------------------------------------------------|----|

| 3.1 | Different PIOs used in the design                                       | 32 |

| 3.2 | CAM modules in the <i>embedded network firewall</i> design              | 37 |

| 3.3 | Netmask RAM memory block usage in the project                           | 43 |

| 3.4 | LEDs function table                                                     | 45 |

| 3.5 | Seven segment status display                                            | 45 |

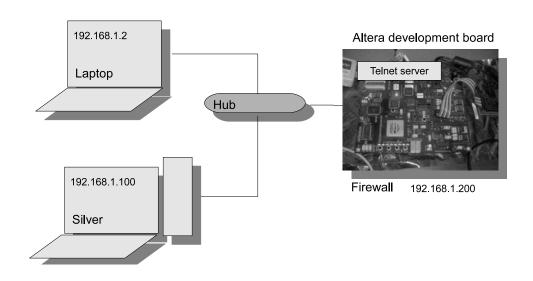

| 4.1 | IP and MAC address table of the device in the testing scenario          | 60 |

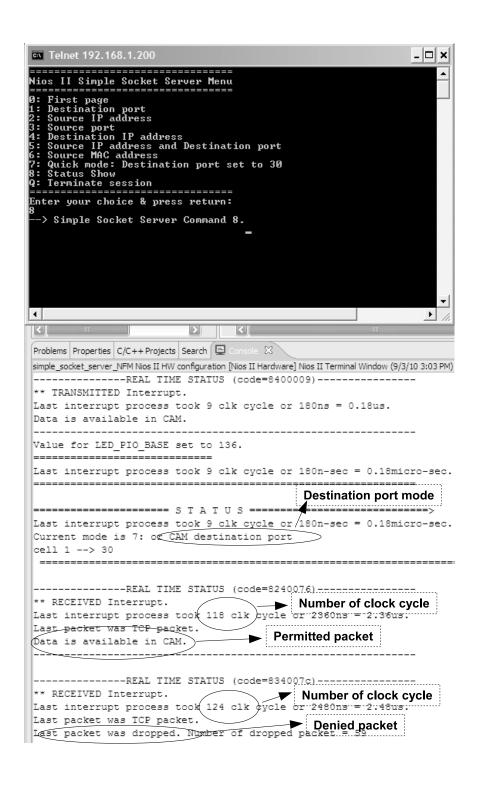

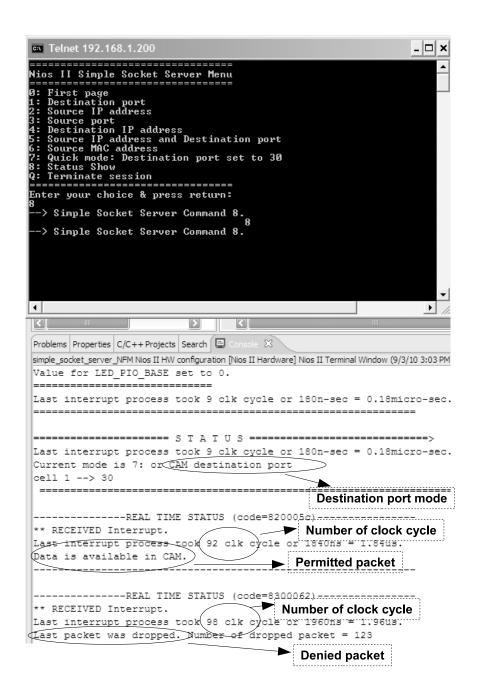

| 4.2 | Interrupt processing time                                               | 72 |

| 4.3 | Number of clock cycles for valid packet processing                      | 75 |

| 4.4 | Number of clock cycles for invalid packet dropping                      | 76 |

| 4.5 | Quartus compilation report                                              | 77 |

| 4.6 | Firewall features                                                       | 78 |

| 4.7 | Number of clock cycles to perform various tasks in the firewall $\dots$ | 79 |

| 4.8 | Processing time                                                         | 79 |

# LIST OF FIGURES

| 2.1  | A firewall is setup to pass only TCP port 80                                        | 8  |

|------|-------------------------------------------------------------------------------------|----|

| 2.2  | OSI and Internet model comparison                                                   | 12 |

| 2.3  | Data encapsulation                                                                  | 13 |

| 2.4  | Inside of a TCP segment                                                             | 14 |

| 2.5  | Inside of a UDP segment                                                             | 15 |

| 2.6  | Inside of an IPv4 packet                                                            | 18 |

| 2.7  | Cost comparison between ASIC and FPGA hardware development [2]                      | 21 |

| 2.8  | Altera development board [3]                                                        | 23 |

| 2.9  | Altera development board                                                            | 25 |

| 3.1  | Embedded network firewall block diagram                                             | 28 |

| 3.2  | Nios II CPU architecture [4]                                                        | 30 |

| 3.3  | CAM 16x8 block diagram (built by dual RAM port)                                     | 35 |

| 3.4  | An example for CAM read and write operation                                         | 36 |

| 3.5  | NFM process flowchart                                                               | 38 |

| 3.6  | Data structure in LAN91C111 on-chip memory                                          | 40 |

| 3.7  | Netmask RAM process                                                                 | 42 |

| 3.8  | Arbiter and connected modules                                                       | 44 |

| 3.9  | LED and seven segment monitoring                                                    | 45 |

| 3.10 | Layered software model for Nios II network application development $\left[5\right]$ | 46 |

| 3.11 | Initialization menu in the Nios IDE console                                         | 51 |

| 3.12 | Firewall Telnet server menu                                                         | 54 |

| 3.13 | Status                                                                              | 56 |

| 4.1  | Test network setup topology                                                         | 60 |

| 4.2  | ICMP request and reply and real time status                                         | 62 |

| 4.3  | Firewall status in the default mode with monitoring                                 | 63 |

| 4.4  | Firewall status in the default mode without monitoring                              | 64 |

| 4.5  | Nmap scanning of the firewall in destination port mode               | 65 |

|------|----------------------------------------------------------------------|----|

| 4.6  | Tcpdump screenshot                                                   | 66 |

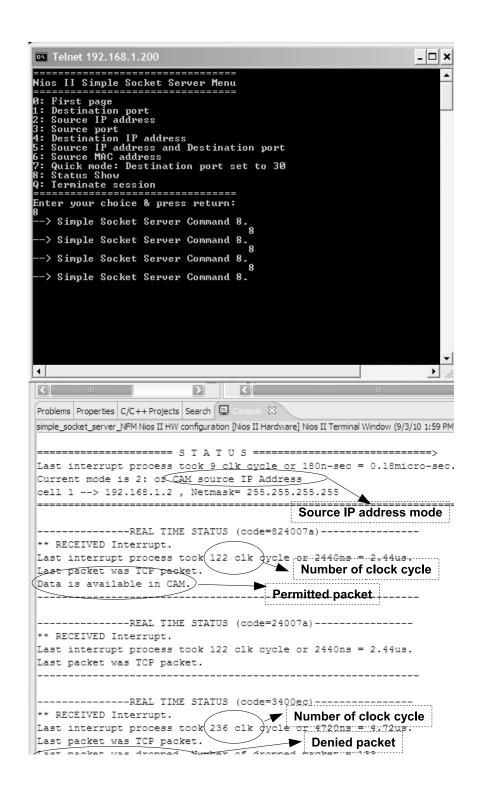

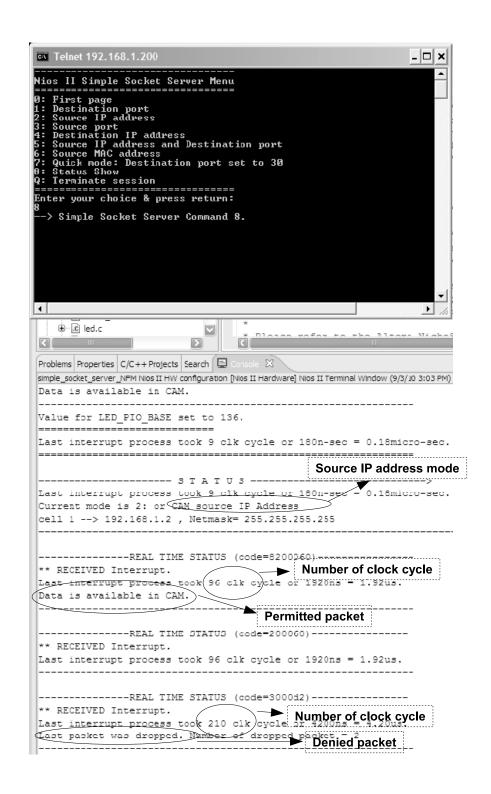

| 4.7  | Firewall in source IP address mode with monitoring                   | 67 |

| 4.8  | Firewall in source IP address mode without monitoring                | 69 |

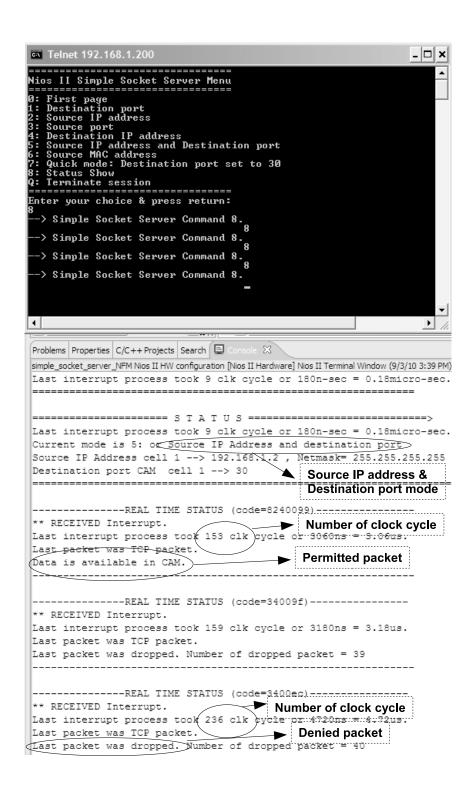

| 4.9  | Firewall in source IP address and destination port number mode with  |    |

|      | monitoring                                                           | 70 |

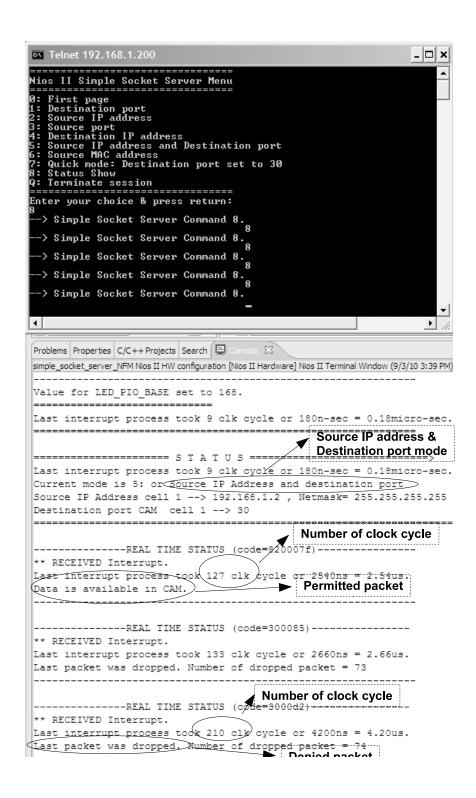

| 4.10 | Firewall in source IP address and destination port number mode with- |    |

|      | out monitoring                                                       | 71 |

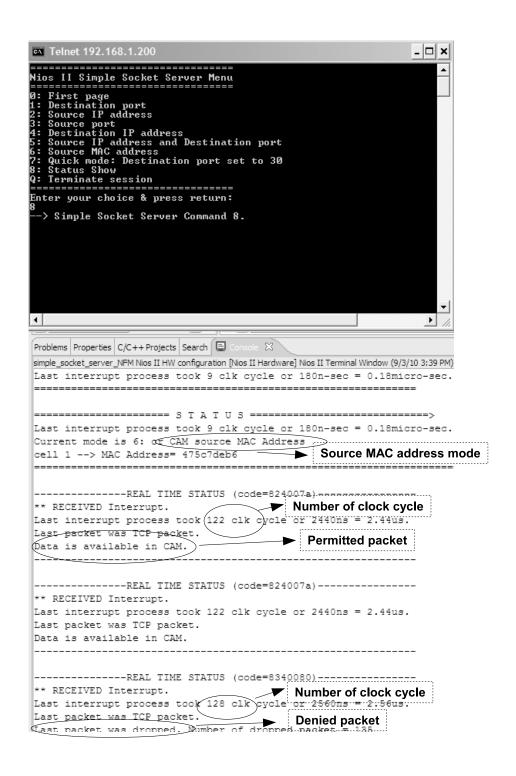

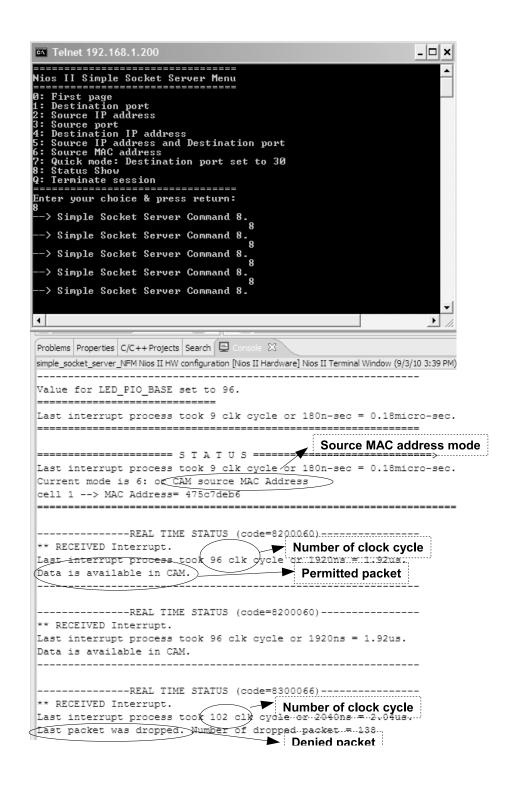

| 4.11 | Firewall in source MAC address mode with monitoring                  | 73 |

| 4.12 | Firewall in source MAC address mode without monitoring               | 74 |

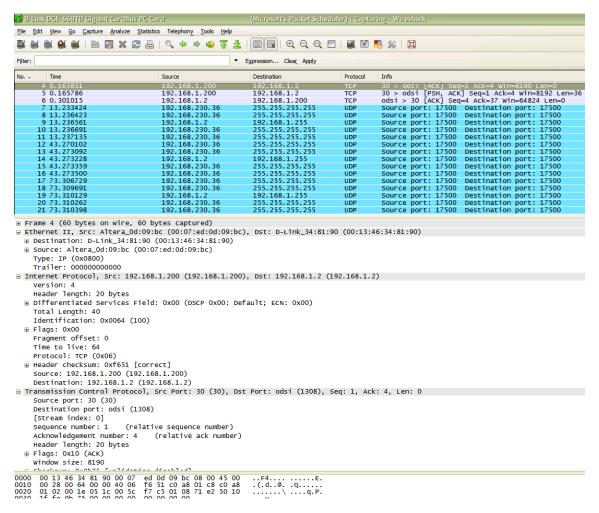

| 4.13 | Wireshark screenshot                                                 | 75 |

# LIST OF ABBREVIATIONS

ACK Acknowledge

AMBA Advanced Micro-controller Bus Architecture

API Application Programming Interface

ARP Address Resolution Protocol

ASIC Application-Specific Integrated Circuit

BSP Board Support Package

CAM Content Associative Memory

CSMA/CD Carrier Sense Multiple Access With Collision Detection

CPU Central Processing Unit

CRC Cyclic Redundancy Check

DARPA Defense Advanced Research Projects Agency

DoD Department of Defense

DMZ Demilitarized Zone

DNS Domain Name System

EDS Embedded Development Suites

ENF Embedded Network Firewall

EPH Ethernet Protocol Handler

FIFO First In First Out

FPGA Field Programmable Gate Array

FTP File Transfer Protocol

HAL Hardware Abstraction Layer

HDL Hardware Description Language

HTTP Hypertext Transfer Protocol

HTTPS Hypertext Transfer Protocol Secure

ICMP Internet Control Message Protocol

IEEE Institute of Electrical and Electronics Engineers

IP Internet Protocol

ISO International Organization for Standardization

ISR Interrupt Service Register

LAN Local Area Network

MAC Media Access Control

NFM Network Firewall Module

OS Operating System

OSI Open Systems Interconnection

PC Personal Computer

PIO Parallel Input/Output

POP3 Post Office Protocol

QoS Quality of Service

RISC Reduced Instruction Set Computing

RTOS Real-Time Operating System

SAN Storage Area Network

SCTP Stream Control Transmission Protocol

SMTP Simple Mail Transfer Protocol

SoC System on Chip

SOPC System On a Programmable Chip

TCP Transmission Control Packet

TCP/IP Transmission Control Packet / Internet Protocol

ToS Type of Service

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

UART Universal Asynchronous Receiver/Transmitter

UDP User Datagram Protocol

WAN Wide Area Network

WWW World Wide Web

### CHAPTER 1

## Introduction

This chapter provides an introduction to network security in computer networking communication. The first section gives the motivation behind this research and why the data protection is very important and vital in today's world of computing. In the next section, the objective of the research is explained and finally, the thesis outline is identified in the last section.

### 1.1 Motivation

Internet has indeed made it effortless for commercial world to do business on the web. This rapid E-commerce expansion has often neglected the security risks that threatens the Internet. Significant number of online applications, such as email clients, web services and database systems supplied by companies' I.T departments, provide services to public which attackers desire to access for destructive purposes. Password attacks, identity theft, business and personal data loss, information manipulation and data corruption are only a glance of damages that are in news headlines. A network administrator or security professional's job is to ensure the safety and reliability of a network from malicious and destructive attacks from the network and network-accessible resources. The security staff need to know how these attacks are being carried and how they can be stopped. Table 1.1 shows the estimated cost of recovery for companies and organizations due to malware attacks [1].

From 2004 onward, the loss declined due to increasing and improving network

**Table 1.1:** Estimation of malware financial impact [1]

| Year | Worldwide impact (US \$) |

|------|--------------------------|

| 2006 | \$13.3 Billion           |

| 2005 | \$14.2 Billion           |

| 2004 | \$17.5 Billion           |

| 2003 | \$13.0 Billion           |

| 2002 | \$11.1 Billion           |

| 2001 | \$13.2 Billion           |

| 2000 | \$17.1 Billion           |

| 1999 | \$13.0 Billion           |

| 1998 | \$6.1 Billion            |

| 1997 | \$3.3 Billion            |

| 1996 | \$1.8 Billion            |

| 1995 | \$0.5 Billion            |

security infrastructure. The growth in network security is the result of research and costly technology the has been involved for hardening the network [6].

A highly effective solution, to protect the internal network from the outside world, is placing a network firewall where the internal network connects to the Internet Firewalls [7]. Basically a firewall is a part of computer networking equipments designed to restrict unauthorized or unwanted access between sections of a network while permitting authorized communication. It can be configured based upon a set of rules and policies in the organization to permit or deny the data passing through; "nothing can be trusted until it's tested". A firewall can greatly reduce attacks to internal resources and overall elevates the site security. Without a firewall, network security can be out of control and practically the damage can be brutal. Although it is possible for an administrator to use available individual software based firewall for each computer in a large size network, but that can be a difficult and time consuming procedure. In reality, it is way more efficient to have a network firewall at gateway of the site rather than protecting each single computer in the network. To a large extent, a network firewall is more powerful and manageable than its smaller

counterpart.

# 1.2 Research objective

The objective of this research is to design an embedded customizable hardware network firewall that can be used on a network gateway (i.e., network router or broadband modem) instead of a dedicated firewall device in order to improve the speed and features accomplished in the other researches in [8], [9].

Cheng in [8] has designed a source Internet Protocol (IP) address based firewall on FPGA that is capable of improving the speed compared to a software based firewall. However, this firewall can only operate in source IP address mode and is not configurable after it is initialized. Laturnas in [9] has improved the FPGA based firewall by speeding up the packet processing time and adding dynamic Content Associative Memory (CAM) expiration, however the firewall still operates in a single mode and can not be configured in real time.

The high speed packet processing firewall, designed in this research, can be configured in different modes and has the ability to accept and apply configuration changes in real-time along with speed improvement compared to [8],[9]. The modes, that this firewall can operate on, are based on header information in Link, Internet and Transport layers of the Transmission Control Protocol/ Internet Protocol (TCP/IP) protocol stack. The following six options are the different modes implemented in the firewall designed in this research:

- TCP/UDP destination port number

- TCP/UDP source port number

- Source IP address

- Destination IP address

- Source Media Access Control (MAC) address

- Combination of source IP address and destination port number

This firewall can be used for various purposes in a network with several applications. The source or destination port filtering is the useful feature for controlling the traffic to a dedicated server. For example, the firewall can be configured and placed in Demilitarized Zone (DMZ) to only permit TCP port 80 and TCP port 443 packets towards a web server which serves up Hyper Text Transfer Protocol (HTTP) and HTTP Secure (HTTPS) requests from users. Source or destination IP address would be beneficial in an organization that would like to permit or deny access for known IP address or a range of IP addresses. There are occasions that a compromised PC inside of a network has to be blocked until further investigation. Source MAC address can be used in this scenario to deny access of that PC to the Internet or other part of the network.

The main block has been built using Verilog Hardware Description Language (HDL) in order to speed up the packet processing. A processor based embedded system with real-time operating system has been designed to achieve highly customized and on the fly configuration change in the firewall. Also CAM has been used to improve performance of packet matching. The whole design has been implemented and evaluated on an Altera Field Programmable Gate Arrays (FPGA) device.

### 1.3 Thesis outline

The key functionalities of the computer network and the network security are given in Chapter 2. Hardware and software components of this design are described in Chapter 3. Chapter 4 focuses on testing and evaluation of the firewall and finally Chapter 5 provides summary of the research, conclusions and suggestions for future work.

# Chapter 2

### BACKGROUND

In this chapter, background information of the computer network, network security and embedded system are presented. The first section discusses fundamentals of networking, specifically TCP/IP networking. The second part talks about network security and different types of risks that are involved, and in the final section, embedded system and FPGA technology are described.

# 2.1 Network security

Corporate networks are valuable assets. While being exposed to the Internet, the network needs to be protected from security threats. A network security manager needs to know what type of risks the network faces and how to defend it from these risks. In the following points, some of the main risks that threat data (information in the computers) and resources (computers themselves) are discussed.

• Viruses, Worms, Trojans, and Malware: Viruses, Worms, Trojans, and Malware are malicious code that are written to spread by themselves, and infect a victim's computer, in order to damage the data or take control of the computer [10]. All of them act in variety of ranges from just annoying the user (pop up messages) to very devastating purpose, such as erasing data and software from the computer. These threats are very difficult to protect through firewall, so scanning software needs to be installed on computers along with other security measures.

- Intrusion: This is the most popular type of attack where an attacker wishes to take control of the computers in a network. Attackers have many methods to intrude, ranging from simply guessing the user name and password of the personnels in company to complicated methods of social engineering [7], [10]. Social engineering attack means that attacker pretends to be someone else in a company, for example trying to ask for help from network administrator to reset his or her password and then with new password, the attacker gets access to computer and other resources in the network. Firewall can not fully protect a network from such intrusion but there are some ways to limit the number of accounts accessing the network from the outside world.

- Denial of service (DoS): The DoS attack occurs when a computer service crashes and can not be accessed by anyone. Basically, the attacker tries to prevent users from using their own resources on the network. This attack can happen by flooding a server with a large number of service requests which ends up swamping the buffer of the server. The server tries to respond to these *Spam* requests but can not cope and as a result it goes down. This type of threat is also very difficult to avoid if a company provides general services, like Email, to outside users. But a well configured firewall can prevent *DoS* to reach critical servers [7].

- Information theft: As obvious from its name, in this type of intrusions, the attacker wants access to the personal information, like peoples' financial information. In this method, the attacker creates an Internet service to capture personal information details and gives that information away, or sells it to unauthorized people. By accessing this information, the attacker can use or sell the data for many illegal purposes. To give an example, compromising an insurance company network could give many confidential information to an attacker. Packet or network sniffing is a very popular and successful method

among the attackers to find out about what information is passing through the Internet to the destination [11], [12], [13]. A properly configured firewall can help isolate critical servers from unauthorized access.

#### 2.1.1 Security model

There are two main models to shield against attacks discussed in previous pages:

- Host security: In this model each single host or computer has to protect itself using a personal firewall, anti-virus, anti-malware and anti-spyware software but it is not a simple task. Today, there are different hosts and operating systems from various vendors which make it difficult for the network administrator to install, update, control and manage all individual hosts on a network. Also, users need some background in information technology and computer security in order to be aware of threats and ways they can protect their resources. This method can be useful in *Small Office Home Office (SOHO)* environment but in a larger network environment these protections are insufficient.

- **Network security**: This model can be very effective in most networks, specifically in large network environment with hundreds or thousands of hosts. This method concentrates on the attack protection over the main *network gateway*, that is connected to the outside world, rather than each single host in the network. This is where firewall enters the battle!

#### 2.1.2 Firewall and traffic control

A firewall is a hardware or software (or combination of both) device on the network that is placed between network segments. It controls the connections that are being made between hosts as well as data flow based on rules and policies defined. Usually the firewall connects the internal network to the Internet and controls the data traffic so that only authorized data would pass through. The firewall inspects the data packet and processes the header information of each packet and determines whether the packet should be passed or dropped according to its policy configuration. This is also called *packet filtering* and it falls under the following categories:

- Source port

- Destination port

- Protocol type

- Source IP address

- Destination IP address

- Source MAC address

- Destination MAC address

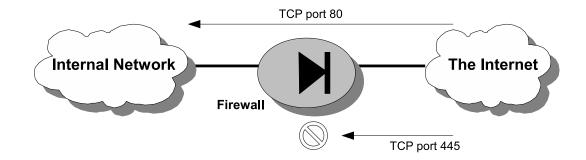

For example in Figure 2.1, TCP port 80 is allowed access to the internal network while the TCP port 445 is not allowed.

Figure 2.1: A firewall is setup to pass only TCP port 80

In the next section, we are going to investigate computer network technology and find out how firewalls work.

# 2.2 Computer networking

A network is a collection of computers and devices connected together in order to communicate with each other and share resources [14]. There are several types of commonly used networks by scale:

- Local Area Network (LAN): The most common type of network for physically close computers and devices to each other.

- Wide Area Network (WAN): A network that connects very long distant computers together.

- Internetworking: Connects two or more private networks via separate infrastructure. *The Internet* is short for inter-networking and is the biggest network entity that is aggregation of many inter networks.

When computers share a network and want to communicate, they must follow certain rules to understand their language or protocol so to speak. Basically, the protocol defines how the communication occurs [15]. To develop and maintain a network as simple as possible, modular concept is used for exchanging data between networking components [14]. It is much easier to break down a big task to some smaller tasks; each module is capable of a single task or related small functions and communicates with other modules. Each individual module does not know the details of how the rest of the modules do their jobs. This method makes each software or hardware module isolated and independent from each other, which means when modification is required, it can be done with least interference. The modular approach has the following benefits:

- The complex network process is segmented into uncomplicated components.

- Changes in a particular module does not impact the overall process.

• The standardization and integration between modules can be easier among the vendors.

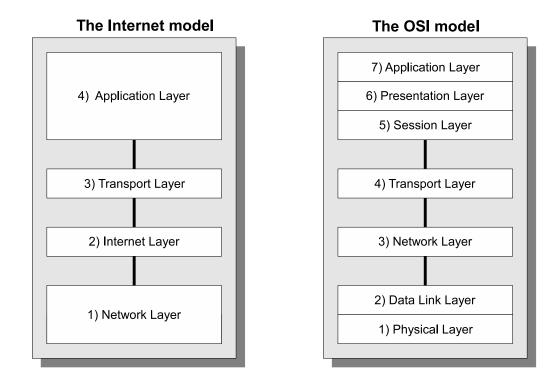

There are two major networking models, The Open Systems Interconnection (OSI) model and the Internet or TCP/IP model. The OSI model, a product of the *International Organization for Standardization (ISO)* [16], sub-divides a networking process into seven smaller sections called layers. Each layer provides services for the direct upper layer and receives services from the immediate lower layer. These layers from the top (closer to the user) to the bottom, are as follows [16]:

- The application layer: Provides data communication between user and network.

- The presentation layer: Provides data translating and formatting from what user understands to what network understands.

- The session layer: Defines functions for starting, controlling and ending communication between hosts in a network.

- The transport layer: Provides data transport management and link reliability which ensures the error correction and flow control by segmentation and reassembly.

- The network layer: Defines logical addressing, routing and packet delivery.

- The data link layer: Responsible for physical addressing and transferring data over physical link.

- The physical layer: Defines specification for physical link.

The Defense Advanced Research Projects Agency (DARPA), a scientific agency of the United States Department of Defense (DoD) introduced the Internet or TCP/IP model during 1970s [17]. The main reason behind creating this model was a need for a robust network that could survive from any disaster such as nuclear war. This model includes of four layers concept [18]:

- The application layer: This layer defines high level protocols to represent, encode and control sessions. To name a few, HTTP, Domain Name System (DNS) and File Transport Protocol (FTP) function are in the application layer.

- The transport layer: The transport layer provides host to host connection establishment and handles flow control. TCP and UDP act in this layer and will be discussed in detail later on.

- The Internet layer: This layer is responsible for logical addressing and routing data across the networks. The main protocol at this layer is the Internet protocol.

- The network access layer: The network access layer handles physical connection to the network medium. Ethernet, Address Resolution Protocol (ARP) and Frame Relay are some protocols that can be found in this layer.

In Figure 2.2, a visual comparison of the OSI and Internet model can be observed. As illustrated in Figure 2.2, the application layer covers the functionality of the application, presentation and session layers of the OSI model. Also, data link and physical layer of the OSI model are correspond to the network access layer of the Internet model.

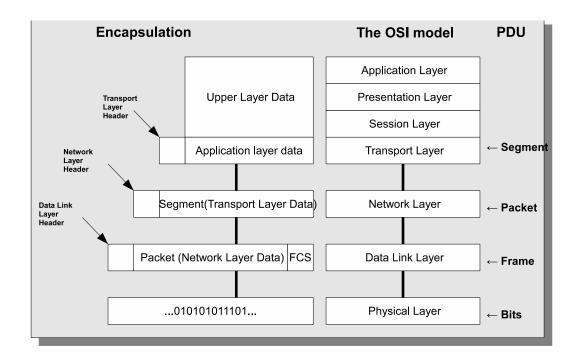

In both models, each layer adds the appropriate information to the data, called header, and sends it to the lower layer at the transmitting host. This process is called *encapsulation*. The reverse process takes place at the receiving host where the header gets extracted and data gets passed to the upper layer. Encapsulation makes it possible for each layer to logically communicate directly with its correspondent. Therefore, from the point of view of each layer, there is no overhead information attached to the data. Figure 2.3 shows the encapsulation in each layer. It would be

Figure 2.2: OSI and Internet model comparison

necessary to mention that, the data wrapped with transport header in the transport layer is called *segment*; segment in network layer is encapsulated with network layer header which creates a *packet*. Packet is encapsulated in *frame* in data link layer and finally frame is passed to physical layer in a bit format (0s and 1s). Combination of layers is called a *stack*. As [14] explains, the OSI model could not be adopted among the vendors because of timing, technology, implementation, and politics problem. The TCP/IP model became very popular; although, the base concept of networking comes from the OSI model.

### 2.2.1 Transport layer

Two important protocols for data transfer are found at the transport layer in the Internet model are Transmission Control Protocol (TCP) and User Datagram Protocol (UDP).

Figure 2.3: Data encapsulation

#### Transmission Control Protocol (TCP)

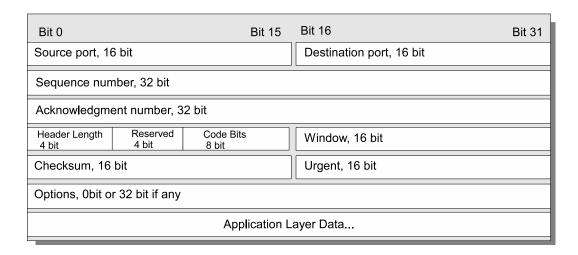

TCP is a connection-oriented transport protocol at the transport layer of TCP/IP model which guaranties data delivery between hosts by creating a virtual circuit and three-way handshake mechanism with transport layer on the other side of the connection. Since Internet layer (IP protocol) does not provide any error detection or data recovery, TCP is an efficient way of communication over unreliable medium. Figure 2.4 shows the details of a TCP segment with the following fields:

- Source port number (16 bit): This number represents the application that data is coming from.

- Destination port number (16 bit): This number represents the application that the data is going to.

- Sequence number (32 bit): Necessary information regarding of the order of the data that is transmitting.

Figure 2.4: Inside of a TCP segment

- Acknowledgment number (32 bit): Shows the next segment that has to be received in the receiver side.

- Header length (4 bit): Total number of bytes in the header field and data.

- Reserved (4 bit): Reserve for future use and set to 0.

- Code bits (8 bit): This field indicates the control bits for session establishment.

- Window (16 bit): Specifies number of bytes to be received before an acknowledgment (ACK) is sent.

- Checksum (16 bit): Shows the calculated checksum of the header field plus data.

- **Urgent (16 bit)**: Urgent bit in the code bits controls this field to show the end of urgent data.

- Options (variable bit): Barely used with some TCP hosts to determine the TCP segment size

• Data: Application layer data.

Port number in TCP header indicates which application or service (in application layer), the data is sourced from and which application or service it is destined for. Applications and protocols such as FTP, HTTP and SMTP require high reliability medium between server and client and TCP protocol provides trustworthy data transmission.

#### User Datagram Protocol (UDP)

UDP is a connectionless and fairly simple protocol compared to TCP at transport layer of the TCP/IP model. UDP does not transfer data as reliable as TCP because in most of today's networking environment, latency and packet loss is very minimal. The UDP protocol was designed to be fast and simple with less overhead. Although UDP communication is prone to errors, there are many applications and services that can tolerate this problem depending on application layer reliability. Figure 2.5 is inside of a UDP segment with the following fields:

| Bit 0                  | Bit 15 | Bit 16                   | Bit 31 |  |

|------------------------|--------|--------------------------|--------|--|

| Source port, 16 bit    |        | Destination port, 16 bit |        |  |

| Length, 16 bit         |        | Checksum, 16 bit         |        |  |

| Application Layer Data |        |                          |        |  |

Figure 2.5: Inside of a UDP segment

- Source port number (16 bit): This number represents the application that the sending host (source) is using.

- Destination port number (16 bit): This number represents the application that the receiving host (destination) is using.

- Length (16 bit): Total number of bytes in header field and data.

- Checksum (16 bit): Shows the calculated checksum to allow the receiver to know if the segment is corrupted.

- Data: Application layer data.

UDP protocol does not need to establish a session before communication begins and does not verify whether the data is received by the recipient (Best effort delivery). This makes it a good choice for the applications and services that verify the data integrity in application layer. DNS, Trivial File Transfer Protocol (TFTP) and Simple Network Management Protocol (SNMP) are few examples that utilize this protocol. Like TCP protocol, port numbers are used by application layer to know which data is coming from which application and where it is going to.

### 2.2.2 Internet layer

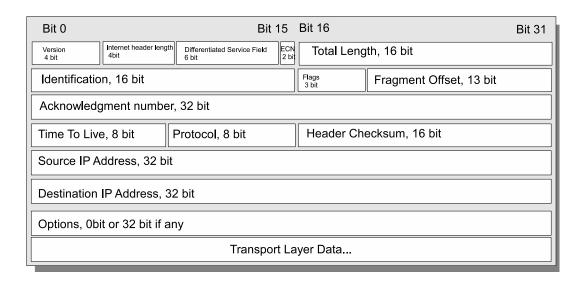

The Internet protocol (IP) is the main protocol in the Internet layer of the TCP/IP model. IP is a connectionless protocol which provides data delivery over the best path in the network using routing protocols. IP is not a reliable protocol and leaves any sort of packet delivery issue such as packet loss, out of order, delayed and duplicated packet to other layers (upper or lower layer). IP does not establish an end to end connection and each packet is sent individually therefore delay or out of order packet delivery could be the result of packets routed over different path. Although this concept may seem very undetermined, there are other protocols in other layers that are capable of fixing this issue and reliably transmit the data. The current IP version 4 is under transition to IP version 6 with many improvements and new features such as 128 bits IP address field instead of 32 bits (in IPv4) providing vastly larger IP address space. Figure 2.6 illustrates the internals of an IP version 4 (IPv4) packet. An IP packet includes the following fields in its header:

- Version (4 bit): Identifies the format of the IP packet.

- Internet header length (4 bit): Represents the length of header.

- Differentiated services field (6 bit): Or also known as Type of Service (ToS) indicates the packet level important to be used in Quality of Service (QoS).

- Explicit Congestion Notification (ECN, 2 bit): Represents the network congestion without dropping packets if both hosts support.

- Total length (16 bit): Represents the total length of the packet including the header and data.

- Identification (16 bit): Same as sequence number in TCP packet.

- Flags (3 bit): Indicates if the packet can be fragmented or not.

- Fragment offset (13 bit): Shows the location of the packet in datagram.

- Time to live (8 bit): Indicates the remaining time of the packet before it is dropped.

- Protocols (8 bit): Represents the type of protocol in higher layer that produced the packet.

- Header checksum (16 bit): Shows the calculated checksum for header only.

- Source address (32 bit): Represents the source IP address (logical address) of the sending host.

- Destination address (32 bit): Represents the destination IP address of the receiving host.

- Options (variable bit): It is normally not used but could contain useful information, for hosts to process the packet.

- Padding (variable bit): Contains some 0s to ensure that IP header is a multiple of 32 bits.

- Data: Transport layer data.

Figure 2.6: Inside of an IPv4 packet

#### Network addressing

Network communication uses address of hosts for data delivery in the network. There are two types of addresses in a network:

• Hardware address: Hardware or physical address was designed in early time of networking to be used in a local network. In such a network the hosts are physically close to each other (LAN). MAC address is the most common type of hardware address in TCP/IP model; it contains six bytes of hexadecimal number, uniquely assigned and hard-coded (can not be changed) for any network adapter by vendors. First three bytes identifies the manufacturer and the rest of the three bytes specifies each network adapter. For example,

00:1A:E3:B7:D7:C8 shows that 00:1A:E3 is the manufacturer ID and B7:D7:C8 is the adapter ID. As mentioned, physical address can only be reached within a local network, therefore it is not accessible from outside of the local network or from another network.

• Logical address: Logical address or IP address is a globally-geographically assigned address for a host in TCP/IP model. It is unique, but temporary per host among all of the interconnected networks. An IP address is a 32 bit decimal number ( along with the network mask ) where each byte is separated with another by a dot. Dots are very good identifiers for identifying networks and hosts when represented with a network mask. For example, the IP 128.233.192.40 with the network mask 255.255.0.0 indicates that 128.233 is a network ID and 192.40 is a host ID.

## 2.3 Embedded systems

An embedded system is a computer inside of a device and is used to run a single task or relatively several smaller tasks, most likely in *real-time* mode. The difference between a PC and an embedded system is that the embedded system is usually a single purpose computer that does not have all of the input and output interfaces like the PC does, for example keyboard and monitor. Usually the embedded system is hidden in the device and its functionality is transparent to the user who uses the device. Embedded systems can be found anywhere; to name a few, cell phone, microwave oven and automobile. Since embedded systems are generally designed to work as a single purpose computer, they don't demand too much hardware resources and therefore they are very efficient in terms of cost, reliability, performance and size.

Every embedded system includes hardware and software. Hardware consists of

a micro-controller or a microprocessor along with peripherals. Additionally, it may contain other hardware blocks depending on the task. Software or running code on the microprocessor in an embedded system is called firmware and is stored on a flash or read-only memory (ROM). The code has to be compiled and debugged by a compiler, an assembler and a debugger tool in a PC and the final executable code is loaded to the embedded system. For more complex systems that run real-time application, a *Real-Time Operating System (RTOS)* is necessary in order to handle task scheduling and prioritizing different tasks [19].

A general method for implementing an embedded system is to combine all of the components on a single chip or *System on Chip (SoC)*. A typical SoC contains one or more processors containing the software, memory block such as ROM and RAM, peripheral like timer, external interface like USB and Ethernet controller. These blocks are connected through a bus, like *Advanced Micro-controller Bus Architecture* (AMBA) bus, inside of the SoC [20]. SoC can be implemented on ASIC or FPGA.

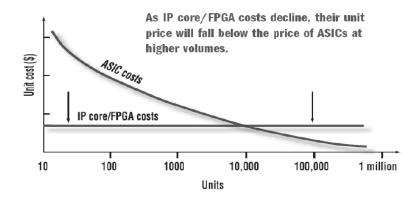

- ASIC: Application Specific Integrated Circuit is an integrated circuit that is fabricated for a specific function. It is intended for making higher volume designs in production which makes it very reasonable due to cost, performance and energy consumption. Once a circuit is fabricated on ASIC, it can not be changed.

- FPGA: Field-Programmable Gate Array is an integrated circuit that is fabricated to be programmed by the designer afterwards. FPGA contains logic blocks and configurable interconnections among the blocks that makes it possible to connect these blocks together. Logic blocks include simple logic gates and may contain memory blocks. FPGAs are multi purpose devices and can be programmed many times for various applications and embedded systems. If lower volume of products are desired, SoC on FPGA is not as costly as SoC on ASIC. In fact, FPGA has many advantages over ASIC. These advantages

are: reconfiguring the FPGA to fix bugs and updating the design, faster time to market and non-recurring engineering costs.

Figure 2.7: Cost comparison between ASIC and FPGA hardware development [2]

Figure 2.7 shows a cost comparison between FPGA and ASIC hardware development. Current leading FPGA manufacturers are Altera and Xilinx with more than 80 percent share of the FPGA market [21]. The most common *Hardware Description Language (HDL)* are *Verilog* and *VHDL* for designing logic circuit. An *Electronic Design Automation (EDA)* proprietary vendor tool is used to compile, simulate, analyze and verify the hardware design and prepare the design for hardware implementation on either FPGA or ASIC.

### 2.3.1 Altera design solution

Altera Corporation is one of the biggest FPGA manufacturers in the world that specializes in system on chip design platform solution. Altera offers various FPGA technologies, software tool and Intellectual property (IP) cores. Cyclone and Stratix series are the main Altera FPGA device families. Stratix is faster, more powerful and more expensive than the Cyclone series [22].

The main EDA design tools from Altera are *Quartus II* and *SOPC Builder*. SOPC builder software is used to connect various hardware blocks and components from the Altera library to make a complete hardware design. These blocks and components can be memory, CPU, interfaces and user designed blocks.

IP cores are already-designed-blocks from Altera to speed up the logic designing and eliminating the cumbersome design process from scratch. The most important IP core from Altera is the Nios microprocessor family which are loyalty free CPUs (for academic research) and are designed by SOPC builder tool incorporated in the Quartus package.

#### Nios II microprocessor

Nios II is a soft core 32 bit RISC microprocessor from Nios CPU family, introduced by Altera as a general processor to be used in Altera FPGA devices to make a complete system on chip design. Nios II is more powerful than the original Nios, its older family member, and gets benefit from the 32 bit instruction set, data and address bus [4].

Nios II can be configured in three different classes to offer more flexibility: fast, standard and economy. Fast architecture uses more resources on FPGA and provides faster speed and best performance in the family, whereas the economy type minimizes the resource and therefore results in a slower CPU. Standard type balances the resource and speed. To make a system based on Nios II CPU, two parts are necessary; SOPC builder is used to generate the hardware part, and *Embedded Development Suites (EDS)* (the software package from Altera) is used to create the software.

#### Altera development board

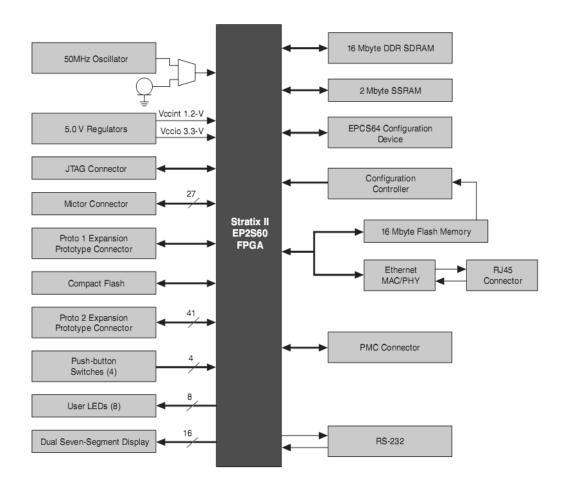

Altera has provided various development boards for designers as a base hardware platform to build, test and debug embedded systems. For the *embedded network*

firewall project, the Stratix II development kit [23] has been used. As shown in Figure 2.8, the development board is equipped with the following components and features [3]:

Figure 2.8: Altera development board [3]

- A Stratix II FPGA with more than 13,500 adaptive logic modules (ALM) and 1.3 million bits of on-chip memory

- Sixteen MBytes of flash memory

- Two MBytes of synchronous SRAM

- Thirty two MBytes of double data rate (DDR) SDRAM

- On-board logic for configuring the FPGA from the flash memory

- On-board Ethernet MAC/PHY device and RJ45 connector

- Thirty two bit PMC Connector capable of 33 MHz and 66 MHz operation

- RS-232 DB9 serial port

- Four push-button switches connected to the FPGA user I/O pins

- Eight LEDs connected to the FPGA user I/O pins

- Dual 7-segment LED display

- Joint Test Action Group (JTAG) connectors to the Altera devices via Altera download cables

- Fifty MHz oscillator and zero-skew clock distribution circuitry

- Power-on reset circuitry

The board (Figure 2.9) has been pre-programmed with a simple web server to respond to HTTP requests from the network traffic coming from the Ethernet port.

#### Nios II software development

Altera provides EDS as a software development environment for the Nios II microprocessor. Code can be written and compiled in a PC and then loaded to the Nios II via a JTAG cable. EDS offers proprietary and open source tools for software creation in the Nios II [24]:

• GNU tool chain is based on a standard GNU library and provides gcc compiler, assembler, linker and *make* procedure in a Unix like environment [25].

Figure 2.9: Altera development board

• Board Support Package (BSP) provides Altera Hardware Abstraction Layer (HAL), Newlib C standard library, device drivers and optional RTOS and optional package like the NicheStack TCP/IP stack in a C/C++ environment.

#### MicroC/OS-II real-time operating system

Altera offers a third party simple and light, yet powerful real-time operating system as part of the BSP which is included in embedded systems that need process scheduling functionality. MircoC/OS-II, from *Micrium*, is a multi-tasking operating system that is mainly used for embedded systems that work in critical safety situation [26]. Altera has recommended to use MircoC/OS-II in any networking related application to make a robust and multi-threaded environment [4].

## Ethernet and the NicheStack TCP/IP stack

Altera provides the NicheStack TCP/IP stack as a light version implementation of TCP/IP stack in BSP. *InterNiche Technologies Inc.* has made this stack for use in

embedded systems with limited memory and processor resources. This stack offers [24]:

- Internet Protocol (IP)

- Internet Control Message Protocol (ICMP)

- User Datagram Protocol (UDP)

- Transmission Control Protocol (TCP)

- Dynamic host configuration protocol (DHCP)

- Address resolution protocol (ARP) for Ethernet

- Standard sockets application programming interface (API)

As described in this chapter, there are technology and tools available to design a firewall depending on the cost and performance speed. The goal of this thesis is to design a low operating cost hardware firewall that is small, operates in an efficient manner and has an acceptable speed processing time while keeping it easy to configure in real-time. Next chapter will walk through the design procedure of this *embedded network firewall* step by step.

## Chapter 3

## Embedded Network Firewall Design

In this chapter, the *embedded network firewall* design is discussed in details. Each individual module and its interaction with other modules in the design is described. In addition to the hardware section, the software part is also presented.

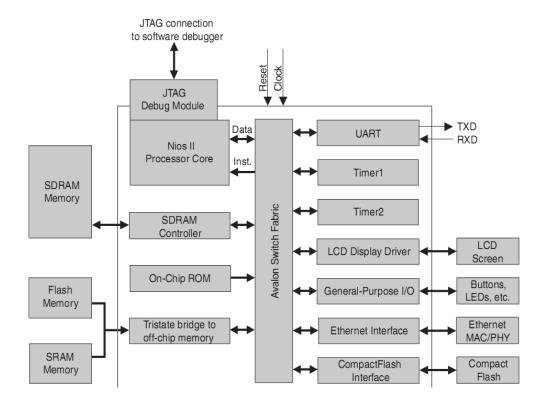

# 3.1 Hardware modules in the embedded network firewall

Figure 3.1 shows the overall layout of the *embedded network firewall* design. As shown in the block diagram, the main modules in the *embedded network firewall* are Nios II 32 bit microprocessor module, Ethernet module, Content Addressable Memory (CAM) module, Netmask RAM module, Arbiter module and Network Firewall module (NFM). All of these modules tightly work together to achieve a powerful, flexible and easy to configure packet filtering firewall.

At the beginning, when the system is powered up, the firewall module is in inactive mode as the Nios II has not been programmed yet to run any code or OS. Nios II Integrated Development Environment (IDE) development tool is used to upload essential applications including RTOS to run on the Nios II. The software initializes all of the modules in the design according to the selected mode of operation. When the Ethernet module finds any TCP/IP traffic targeted toward the Nios II, it interrupts the NFM. In the next step, the NFM extracts the necessary field (based on

Figure 3.1: Embedded network firewall block diagram

the initial operation mode) off the Ethernet frame and inquires the permission from the CAM module. If the CAM module finds the selected field in its memory block (match found), it gives the pass permission to the NFM and the NFM interrupts the Nios II for a receiving packet. In the case of an invalid packet, the NFM drops the packet and waits for the next interrupt from the Ethernet. After each Ethernet interrupt, the packet status is reported to the Nios II by the NFM for monitoring purposes. The firewall operation mode and configuration can be changed any time on the fly by Telnetting to the Telnet server running on the Nios II. Following sections will explain each module functionality in more details.

## 3.1.1 Nios II microprocessor module

As briefly described in the background chapter, Nios II is a 32 bit RISC general purpose soft core microprocessor which is widely open to be customized in any Altera based embedded system design. A designer can choose from fast, standard or economy Nios II reference designs which are included in Altera development tool kit. If the cost or performance can not be met using any of these three reference designs, then the CPU can be customized in SOPC builder as required. In the embedded network firewall project, Nios II standard reference design has been utilized. It only takes less than 5 percent of the FPGA (StratixII 2S60) resources in the development board. Figure 3.2 shows the components in standard reference design. Nios II standard core employs the following properties [3]:

- Thirty two bit instruction set, data and address bus. Instruction set and data bus are separate (Harvard architecture [27])

- Avalon instruction set bus to memory components and Avalon data bus to memory and peripheral components

- Runs at 165 MHz speed

- One hundred twenty seven *Dhrystone Million instructions per second (DMIPS)* considering hardware multiply option

- 5 stage pipelining

- Can access up to 2Gbytes of external memory

- Arithmetic improvement by supporting multiply, divide and shift hardware blocks

- Support JTAG debug module

Figure 3.2: Nios II CPU architecture [4]

Like any other micro-controller the standard Nios II reference design comes with several peripherals. Compared to other micro-controllers, Nios II embedded system environment makes it more flexible and easier for peripheral customization. In the Nios II architecture, both memory and peripheral Input/Output are mapped into one integrated address space. Some of the peripherals play highlighted roles in the embedded network firewall project, and their features will be described in more detail.

JTAG Universal Asynchronous Receiver/Transmitter (UART) peripheral is a character media used to communicate between a PC and JTAG circuitry in Altera FPGA. Also Nios II uses a device driver to manage connection for displaying JTAG data stream on the screen. UART peripheral provides RS-232 character serial communication between Nios II and external device such as terminal software on a host PC.

The Parallel Input/Output (PIO) peripheral provides I/O access to external device, for example hardware custom block, controlling LEDs or seven segment display. In the embedded network firewall project ten different PIOs have been used as follows:

- Button PIO as control commands for troubleshooting and debugging the design (displaying selected header field on seven segment and passing invalid packet)

- LED PIO to show packet status (i.e., ARP, ICMP, TCP or UDP ), status of data availability in CAM or dropped packet

- Seven segment PIO to show selected field in the Ethernet frame and TCP/IP packet

- Two PIOs as control signal between the Nios II and the NFM

- CAM data bus PIO between the NFM and the CAM module

- CAM Address bus PIO between the NFM and the CAM module

- CAM control bus PIO between the NFM and the CAM module

- Status PIO to report the status of the last received packet from the NFM to the Nios II

- Expanded CAM data bus PIO between the NFM and CAM module for storing MAC address

Table 3.1 shows the address mapping for each peripheral in the *embedded network* firewall design. One of the most important peripheral modules in the *embedded* network firewall project is the Ethernet module that will be discussed in detail in the next section.

**Table 3.1:** Different PIOs used in the design

| Block              | Name                 | Physical address |

|--------------------|----------------------|------------------|

| JTAG core          | JTAG_UART            | 0x021208b0       |

| Ethernet           | LAN91C111            | 0x02110000       |

| LCD display        | LCD_DISPLAY          | 0x02120880       |

| UART               | UART1                | 0x02120840       |

| Button             | BUTTON_PIO           | 0x02120860       |

| LED                | LED_PIO              | 0x02120870       |

| JTAG UART          | JTAG_UART            | 0x021208b0       |

| NFM (from Nios II) | PIO                  | 0x01200020       |

| NFM (to Nios II)   | PIO_1                | 0x01200030       |

| CAM                | PIO_DATA_OUT_CAM     | 0x01200040       |

| CAM                | PIO_ADDR_BUS_CAM     | 0x01200050       |

| CAM                | PIO_CTRL_CAM         | 0x01200060       |

| CAM                | PIO_STATUS           | 0x01200070       |

| CAM                | PIO_DATA_OUT_CAM_MAC | 0x01200080       |

#### 3.1.2 Ethernet module

Altera development board comes with networking capability and is equipped with LAN91C111 chip from Standard Microsystems Corporation (SMSC) [28]. LAN91C111 control and data pins are hardwired to the FPGA on the development board, and tools are available for Nios II embedded system to communicate with network through the chip. This chip includes MAC and PHY engines and is able to process Carrier Sense Multiple Access With Collision Detection (CSMA/CD) protocol in 10/100 Mbps full duplex. The chip has 8 KBytes of internal memory for receiving and transmitting operations; also there are 32 registers in the chip for configuring and controlling the operations. The chip must be initialized by the Nios II for receiving and transmitting operations. The initialization sets some parameters, such as MAC address, memory base address (to be accessed by Nios II) and speed negotiation. Two main operations are packet receiving and packet transmitting:

• Packet receiving: When the receive interrupt flag is enabled and the receive queue is empty in on-chip memory, the data is written to assigned memory

with a packet number as soon as there is an incoming packet on the Ethernet interface with matching address. After packet reception ends, the status word (for the receiving operation) is written at the beginning of the packet. If there is an error in reception or Cyclic Redundancy Check (CRC) error in the frame, the packet is dropped and memory is released, otherwise the packet number is written at receiving First In First Out (FIFO) buffer and an interrupt is made to notify the Nios II for packet receiving. Now the device driver in Nios II processes the data in receiving area and releases the memory.

• Packet transmitting: At the beginning of the packet transmission, the device driver attempts to allocate memory in on-chip memory block. When it happens, LAN91C111 interrupts the device driver for a successful memory allocation and a transmit packet number is generated. In the next step, transmit packet number is written into transmit FIFO by the device driver and waits until LAN91C111 accomplishes the transfer. After the transfer completes, the status word is placed at the first word in the memory and the packet number is moved to transmit completion FIFO, and an interrupt is made to notify the Nios II for transmission completion. The device driver reads the interrupt status word to check if the transmission is successful or failure.

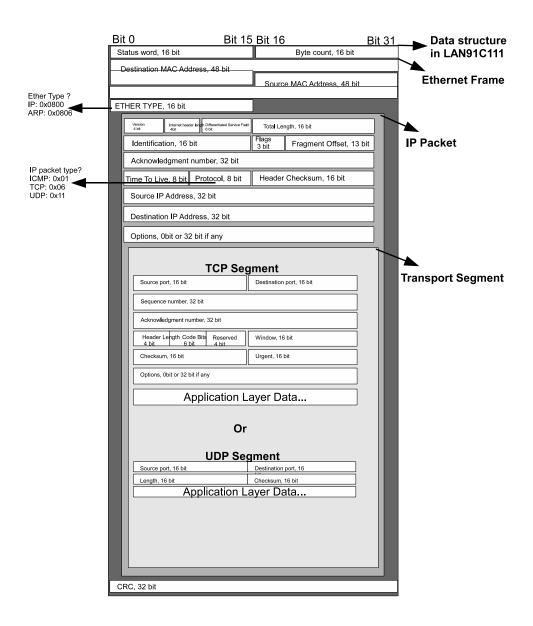

The data structure in on-chip memory for both receiving and transmitting locations begin with the status word which is written by MAC engine upon receiving or transmitting operation. The next word shows the number of the data bytes that are written by the MAC after the packet is received, and by the Nios II after the packet is transmitted, and the actual Ethernet frame comes after the byte count. In case of the received frame, the last byte in the data is the CRC which is followed by a control byte (Figure 3.6). In the development board, the Flash memory and LAN91C111 share the data and address bus, and all of the LAN91C111 registers can be accessed from 0x300 address offset. The 16MByte Advance Micro Device (AMD)

flash memory on the board can be used for holding FPGA configuration and also for general purpose non-volatile memory storage for the Nios II micro processor, for example the Nios II software.

## 3.1.3 Content Associative Memory module

Content Associative Memory (CAM) is a type of memory system for fast searching application in hardware [29]. It acts differently from the other types of memory like RAM and ROM. Unlike other memory systems, CAM is fed with data instead of address. CAM searches the entire memory for data and if the data is available in memory (data already stored previously), the location of data is returned. Since the whole operation takes only one clock cycle, CAM requires memory cell and associative comparison hardware circuitry for conducting parallel search of each memory cell. This makes CAM very fast but also costly due to consumption of large number of hardware logic blocks. Because of the high speed data search, CAM is widely used in networking devices such as firewalls, network switches and routers, offering fast address lookup and low packet processing latency.

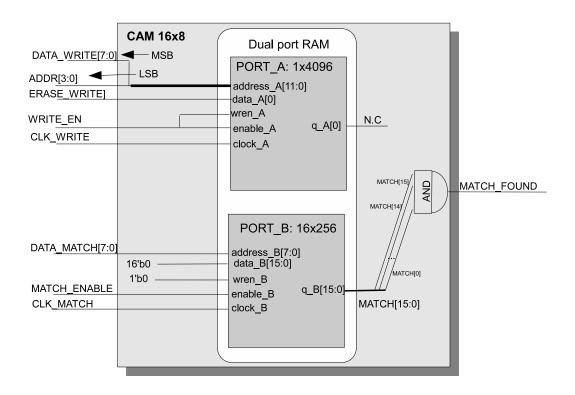

In the *embedded firewall*, CAM is used for saving source and destination TCP/UDP port number, source and destination IP address and MAC address field. Altera does not provide any CAM memory block on the StratixII FPGA device or IP core implementation in the Quartus II package, therefore dual port memory with some extra logic has been used to implement the CAM modules for network firewall design [29]. The CAM template module is a 16 word by 8 bit (CAM 16x8) in total of 128 bits and is made by a 4 Kbits of dual port memory block on FPGA. Figure 3.3 shows the CAM 16x8 block diagram and its internal dual port RAM block wiring.

The 4 Kbit memory block is setup as a 1 bit data and 12 bit address bus input for port-A and 16 bit data and 8 bit address bus for port-B. Port-A is used for data write operation with an asserting "1" on the data input as write enable signal for

Figure 3.3: CAM 16x8 block diagram (built by dual RAM port)

CAM module, and concatenating 8 bits of data and 4 bits of address in address port of port-A. Port-B is used for data read operation with an asserting "0000 0000 0000 0000" (16'b0) in data input of port-B and providing the desired data at data input of the CAM module. CAM write and read operations are briefly explained in next paragraph by using an example.

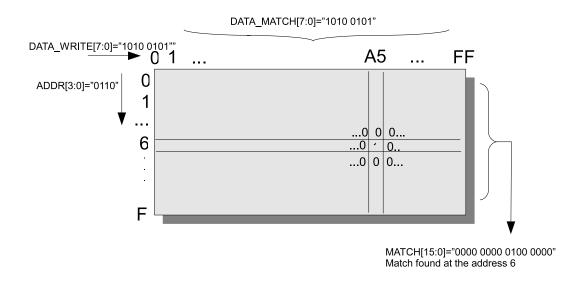

- CAM write operation happens by providing the data and address to the DATA\_WRITE (as MSB) and ADDR (as LSB) input of the CAM module which makes "1" being written at "DATA\_WRITE, ADDR" location of memory. For example, one would like to store A5h value at the 6th memory location in the CAM; "1010 0101, 0110" is provided to "DATA\_WRITE, ADDR", therefore 1 is written at "1010 0101 0110" location (or at the address 2646 in the memory).

- CAM read operation is done by providing the value to DATA\_MATCH input

of the CAM and enabling the CAM read enable input. If the data is already written in the CAM, the location appears in the MATCH output of the CAM module. For example one would like to find out whether A5h value is stored in the CAM or not. A5h is provided to the DATA\_MATCH input of the CAM which causes the A5h memory location to be searched and the corresponding data, which is "0000 0000 0100 0000" (6th bit of MATCH goes high), is returned at the MATCH output. The output is the same as address location which the data was previously written at.

Figure 3.4: An example for CAM read and write operation

Figure 3.4 shows the discussed example. In the *embedded network firewall* design two CAM 16x16 modules are used to store sixteen 16 bit destination and source port numbers, two CAM 16x32 modules are used to store sixteen 32 bit destination and source IP address and one CAM 16x48 module is used to store sixteen 48 bit source MAC address by cascading several CAM 16x8 modules. Total of eighteen 4 Kbits of memory blocks on the FPGA are exhausted for the CAM modules. Table 3.2 summarizes all of the CAM modules in the *embedded network firewall* design.

Table 3.2: CAM modules in the embedded network firewall design

| Mode                   | Capacity | Size   | Component  | Memory block |

|------------------------|----------|--------|------------|--------------|

| Destination port       | 16 word  | 16-bit | 2 CAM 16x8 | 2*4Kb        |

| Source port            | 16 word  | 16-bit | 2 CAM 16x8 | 2*4Kb        |

| Destination IP address | 16 word  | 32-bit | 4 CAM 16x8 | 4*4Kb        |

| Source IP address      | 16 word  | 32-bit | 4 CAM 16x8 | 4*4Kb        |

| Source MAC address     | 16 word  | 48-bit | 6 CAM 16x8 | 6*4Kb        |

## 3.1.4 Network Firewall Module (NFM)

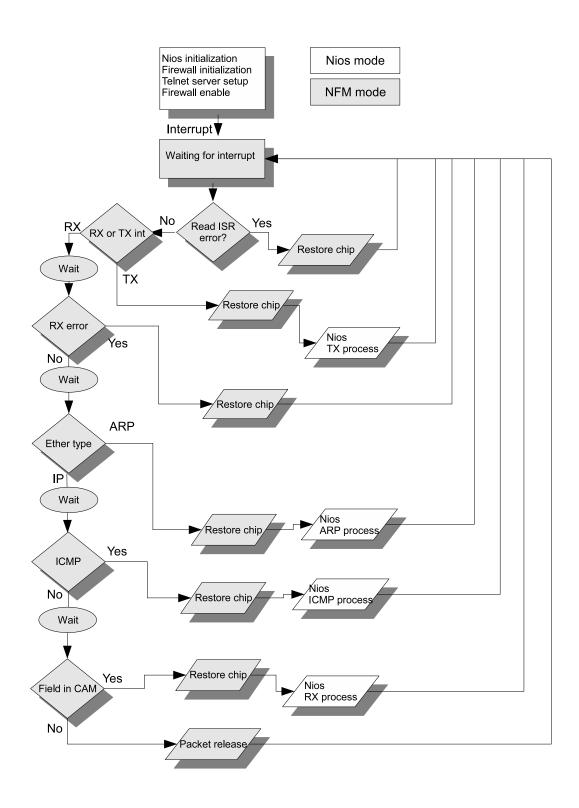

The main functionality of the *embedded network firewall* project is accomplished by the network firewall module (NFM). This Verilog module contains a state machine with five states. The machine changes the state from one to another based on the input signals and current conditions. After system initialization and enabling the firewall by the Nios II, the NFM waits for an interrupt from the Ethernet module. Figure 3.5 illustrates the NFM process flowchart.

- Interrupt process state: When an interrupt occurs, at first the NFM saves current value of the registers in the Ethernet module and then reads the *interrupt status register (ISR)*. If the status register indicates any error, such as receive over-run error or Ethernet Protocol Handler (EPH) error, the state machine switches to the Restore chip state and all of the registers are restored to their previous values and the Nios II takes over the error handling process. If the status register shows the transmit interrupt, the state machine switches to the Restore chip state and the Nios II takes over the interrupt. In case of the receive interrupt, the state machine switches to the Receive state for receiving process.

- Receive state: In this state, the first word from the beginning of the receive data queue is fetched in order to investigate if there is any issue in the frame reception. The error can be of Alignment, bad CRC, Long length frame or

Figure 3.5: NFM process flowchart

short length frame. The state machine switches to the Restore chip state for error handling in case of any error otherwise it switches to the Packet type state to discover the type of the Ethernet frame. In the next step, according to the firewall condition, specific data field is extracted from the packet (for example destination TCP port number) and is sent to the corresponding CAM module for a match. If the data field is already put in the CAM in the initialization/configuration stage (therefore is available), then the CAM indicates match found signal and the state machine switches to the Restore chip state and Nios II is notified by an interrupt of a valid receiving packet. If the data is not available in the CAM, the state machine switches to the Release packet state to drop the packet. In the source MAC address mode, the firewall acts in opposite way meaning that it drops the frame if the source MAC address is found in the CAM. This mode is useful when a host communication has to be denied in a local network to prevent spamming until further action is taken by the network administrator.

• Packet type state: This state discloses the type of the Ethernet frame (Ethertype filed in the Ethernet header). If the receiving frame is an Address Resolution Protocol (ARP) frame, which is used to translate an IP address to a MAC address in a local network, the interrupt handling is done by the Nios II by switching to the *Restore chip state*. If the frame data is not an ARP then the packet is considered to be an Internet Packet (IP) and it is investigated for Internet Control Message Protocol (ICMP) packet. Figure 3.6 illustrates all of the fields inside of the memory structure in LAN91C111; the *packet type state* extracts a few of these fields based on the firewall configuration.

In this design, for the sake of troubleshooting, all of the ICMP packets are forwarded to the Nios II for ICMP response and therefore the state machine switches to the *Restore chip state*. The firewall ICMP handling can be disabled

Figure 3.6: Data structure in LAN91C111 on-chip memory

by the user to speed up the packet processing since several clock cycles need for identifying the ICMP packet by the NFM. In the next step based on the firewall condition, specific data field is extracted from the packet and the state machine switches back to the *Receive state*.

- Release packet state: When the state machine lands in this state, it means the packet cannot make it to the network beyond the firewall and must be dropped. This action is followed by switching back to the Restore chip state.

- Restore chip state: At this state the *pointer register* and *bank select register* are restored to their value before the *Interrupt process state*.

- Wait state: In the development board design, the ARDY pin of LAN91C111 is not connected to the FPGA and according to the Ethernet manufacturer, any read operation from the receive FIFO should not be done for at least 370 ns after the pointer register is filled with the data register. The board operates at 50 MHz and thus each clock cycle takes 20 ns to be completed, so each read operation has to wait at least 19 clock cycles (or 380 ns) for a safe reading. The wait state idles the NFM for 19 clock cycles until the data register output is valid.

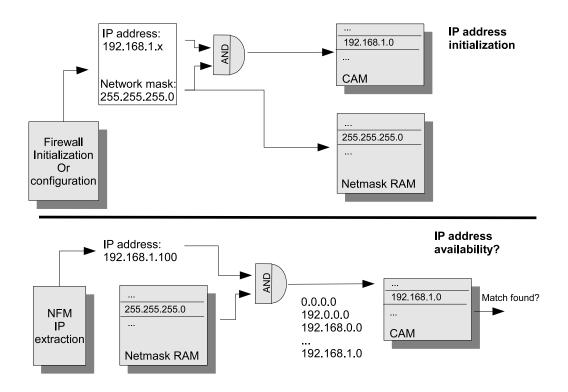

#### 3.1.5 Network mask RAM module

In the source and destination IP address condition, the firewall can not only permit or deny a single IP address, but it can also decide what range of IP addresses can access the network beyond the firewall. This can be possible by either entering every single IP address in the source or destination IP address in the CAM module, or by specifying an IP range (network ID and network mask). As it sounds the first option is not efficient because it is a tedious procedure for entering all of the IP addresses into the CAM and needs lots of valuable CAM memory cells. In this project the

second option is selected by sacrificing a few clock cycles to search in RAM module for network mask. CAM is not capable of storing don't care bit, therefore, the combination of CAM and netmask RAM make it possible for storing the IP address range. Every single location of the netmask RAM module is pulled and tested against the data stored in the CAM IP module and as soon as a match is found, the packet is validated and passed through the firewall. If no match is found in the CAM, the IP address has not been configured in the permitted IP address range and hence the packet must be removed. If there are more data fields in the netmask RAM, this procedure takes more clock cycles to finish.

The *embedded network firewall* project employs two RAM modules, each with sixteen 32 bit words to store network mask for source and destination IP addresses. Figure 3.7 illustrates an example of network mask function. Table 3.3 shows the RAM modules used in the network firewall design.

Figure 3.7: Netmask RAM process

**Table 3.3:** Netmask RAM memory block usage in the project

| Mode                   | Capacity | Size   | Component   | Memory block |

|------------------------|----------|--------|-------------|--------------|

| Destination IP address | 16 word  | 32-bit | 1 RAM 16x32 | 1*1Kb        |

| Source IP address      | 16 word  | 32-bit | 1 RAM 16x32 | 1*1Kb        |

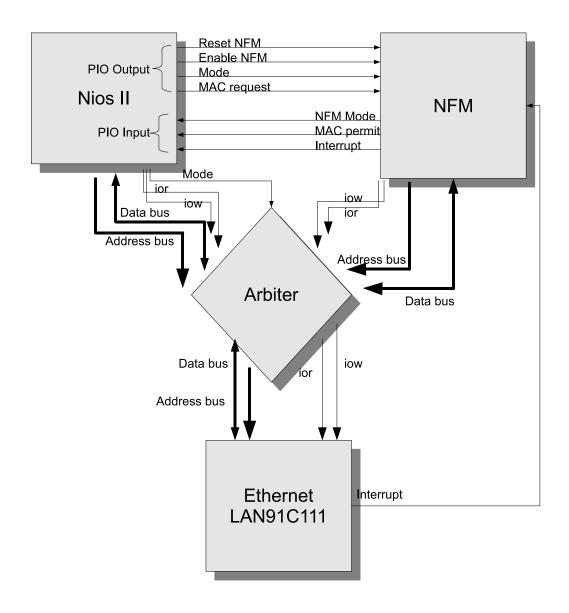

#### 3.1.6 Arbiter module

So far we have seen the NFM interferes the data communication between the Nios II and the Ethernet module in order to enforce the firewall policy. Obviously, the data transfer can only happen among these modules when there is a shared data and address bus. Arbiter comes as a control module to allocate shared resources (Ethernet module) between the Nios II and the NFM modules and lets only one to one communication at a time. In this design, two modes are used to differentiate when the Nios II is using the Ethernet module and when the NFM is in charge of the Ethernet module. The first mode is called software mode or Nios mode and second mode is called hardware or NFM mode. Software mode is the default mode until the firewall is activated, from then onwards if the Nios II wants to communicate with the Ethernet module, it has to make a request to the NFM. The NFM acknowledges and allows the request when it is in idle mode and no interrupt is being processed. Figure 3.8 shows a block diagram of the arbiter and its related modules. Ethernet module and the Nios II data bus are bi-directional. The arbiter uses tri-state buffer, which is controlled by mode signal from the Nios II to allocate the data bus.

# 3.1.7 Status display module

This module is designed in the *embedded network firewall* project to let the user/administrator observe the visual status of the last processed packet. Four push buttons on board are used to select output PIO from the NFM to be shown on the LEDs and seven segment display. Table 3.4 shows the LED status table and Figure 3.9 while

Figure 3.8: Arbiter and connected modules

the display are in action. The *clk\_cycle\_counter* is the binary counter for showing the number of clock cycles used for the last interrupt processing.

Figure 3.9: LED and seven segment monitoring

Table 3.4: LEDs function table

| LED number | SW 0 pressed         | SW 0 not pressed |

|------------|----------------------|------------------|

| LED 0      | clk_cycle_counter[0] | ISR_register[0]  |

| LED 1      | clk_cycle_counter[0] | permitted packet |

| LED 2      | clk_cycle_counter[1] | ARP packet       |

| LED 3      | clk_cycle_counter[2] | ICMP packet      |

| LED 4      | clk_cycle_counter[3] | TCP packet       |

| LED 5      | clk_cycle_counter[4] | UDP packet       |

| LED 6      | clk_cycle_counter[5] | MATCH found      |

| LED 7      | clk_cycle_counter[6] | Dropped packet   |

Table 3.5 indicates the seven segment display status. IP address in Table 3.5 is shown in *a.b.c.d* format and MAC address in *aa:bb:cc:dd:ee:ff* format. Only last 4 Bytes of the MAC address can be displayed on the seven segment display.

Table 3.5: Seven segment status display

| SW 2 | SW 3 | src/dst port | src/dst IP addr | src MAC addr           |

|------|------|--------------|-----------------|------------------------|

| 0    | 0    | port number  | d               | ff                     |

| 0    | 1    | -            | С               | ee                     |

| 1    | 0    | -            | b               | $\mathrm{d}\mathrm{d}$ |

| 1    | 1    | -            | a               | cc                     |

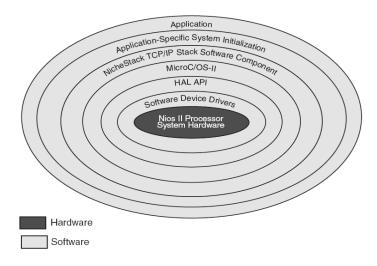

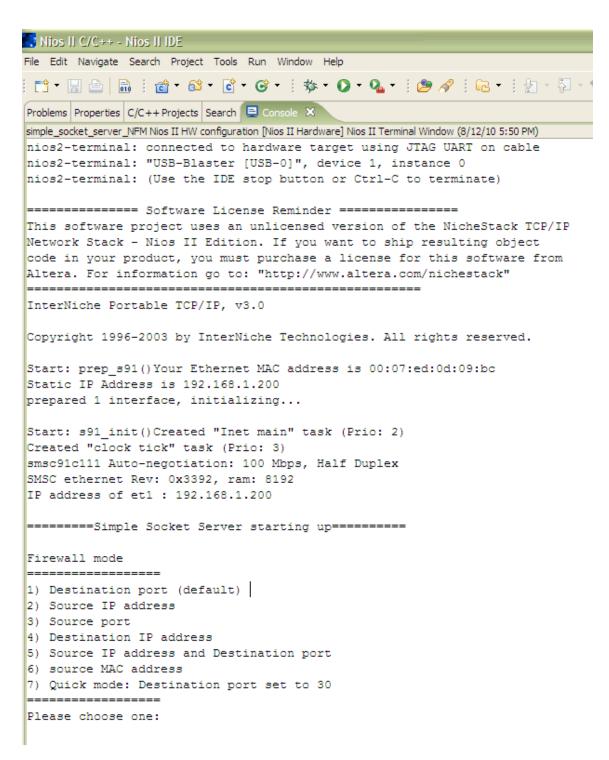

# 3.2 Software modules in the embedded network firewall