# Operational Phase-Space of Separation by Plasma Implantation of Oxygen (SPIMOX)

S. Sundar Kumar Iyer, Xiang Lu, Jingbao Liu, Barry Linder, Chenming Hu, Nathan W. Cheung Plasma Assisted Materials Processing Laboratory, Dept. of EECS University of California at Berkeley Berkeley, CA 94720, USA

> Jing Min, Zhineng Fan and Paul Chu Department of Physics and Material Science City University of Hong Kong Kowloon, Hong Kong

Abstract -- SPIMOX using plasma immersion ion implantation (PIII) has been proposed as a cost-effective method for fabricating silicon on insulator (SOI) wafers. PIII, compared to conventional implanters, allows for simpler and low maintenance-cost implanters. High throughput, independent of the wafer size can be achieved by the SPIMOX process. A phase-space of implantation time and implantation pressure is developed to determine the operational regions for SPIMOX implantation. SPIMOX process using high fractional ionization plasma for implantation is found to be particularly suited for thin SOI fabrication required for future low-power IC applications.

## I. INTRODUCTION

Silicon on insulator (SOI) has an important role to play in the low-power, low-voltage IC technology [1]. Separation by implantation of oxygen (SIMOX) is a popular technique for fabricating SOI wafers. In this technique, oxygen 1s implanted using conventional implanters in a silicon wafer. The implanted wafer is then annealed at a high temperature of 1320 °C for 6 hours to obtain a continuous buried oxide layer The typical and single crystalline top silicon layer. implantation voltage is 190 kV and the implantation dose is 1.8x10<sup>18</sup> cm<sup>-2</sup>. This gives a buried oxide of thickness 380 nm with a silicon overlayer thickness of 210 nm [2]. Using a top of the line high current implanter with an ion current of 200 mA, the time taken to implant a 200 mm diameter wafer is about 8 min. Due to the long time taken to implant the wafer, the throughput of the SIMOX is limited. The throughput becomes lower with increase in wafer area. Such high current implanters are costly and have high maintenance costs which also adversely affect the cost of SOI production.

This work is supported by Joint Services Research Program, contract number F49620-94-C-0038 and National Science Foundation, grant number ECS-92-02993.

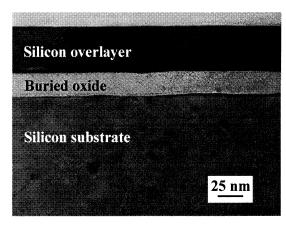

Fig. 1. XTEM of the SPIMOX sample produced at Berkeley. Implantation was done at 60 kV in an  $\Omega_2^+$  dominant oxygen plasma.

Separation by plasma implantation of oxygen (SPIMOX) has been proposed as an alternative method for fabricating SOI wafers [3]. This process uses plasma immersion ion implantation (PIII) [4] technique to implant the oxygen required to form the buried oxide layer. As the whole wafer is implanted simultaneously, the throughput of wafer implantation in PIII is independent of wafer size and can be made much higher than in conventional implanter. The implantation set-up used for PIII is simpler than the conventional high current implanters and hence easier to install and maintain. These factors point to an economical method of fabricating SOI wafers with SPIMOX. The SPIMOX process has been demonstrated as a feasible process for fabricating the SOI structure [3,5]. An XTEM of a SPIMOX sample fabricated at Berkeley is shown in Fig. 1.

In this paper, the implantation process and requirements for SPIMOX formation are briefly discussed followed by the relationship between implantation parameters and SOI dimensions. For a given dose and implantation voltage, an operational phase space is developed using the required implantation time  $(t_{\rm imp})$  and chamber-pressure (p) as variables. The effect of fractional ionization of the plasma on

the operational region in phase space is studied. It is seen that SPIMOX using high fractional ionization is particularly suited for fabricating thin SOI wafers. The time for implantation is limited mainly by the heat dissipation capacity of the wafer holder.

#### II. IMPLANTATION PROCESS INSPIMOX

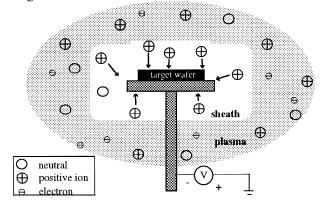

SPIMOX uses PIII for the implantation of oxygen [3]. The target wafer is immersed in a plasma of either oxygen or water. A negative dc bias is applied to the wafer which repels the electrons and forms a positively charged sheath around the wafer. The positive ions are accelerated across the sheath and are implanted in the wafer (Fig. 2). The sheath voltage drop is nearly equal to the applied bias voltage.

Fig. 2. Schematic of oxygen implantation an  $O_2^+$  dominant oxygen plasma for SPIMOX implantation ( $t_{inp}$ ).

The nucleation of oxide below the silicon surface is more probable where the oxygen concentration is higher. Thus to obtain a continuous buried oxide after annealing, the implantation profile of oxygen must be single peaked at the depth of the desired buried oxide. To ensure this, the plasma used for implantation must be dominant in a single ion species and the ion implanted must be monoenergetic. In the Berkeley implanter, the ECR plasma source is tuned to obtain an O2+ dominant oxygen plasma for SPIMOX implantation. The implantation is kept monoenergetic by making the sheath collisionless. This is done by operating at low pressures to ensure that the mean free path of ions for interaction with neutrals is larger than the sheath width for the applied voltage. Use of dc bias for implantation as opposed to pulsed bias helps avoid intermediate energy implants during voltage transitions

# III. IMPLANTATION PARAMETERS

The implantation parameters in SPIMOX are implantation voltage  $(V_0)$ , implantation dose  $(D_0)$ , time taken for implantation  $(t_{imp})$  and chamber pressure during implantation (p).

The silicon overlayer thickness ( $t_{Si}$ ) and the buried oxide thickness ( $t_{BOX}$ ) can be correlated to  $V_0$  and  $D_0$  by (1) and (2).

$$R_{\rm p}(V_0) = t_{\rm Si} + 0.5 \frac{t_{\rm BOX}}{2.2}$$

(1)

where to the first order, the buried oxide center is assumed to be located at the implantation range corresponding to the dominant ion species. The factor 2.2 is to account for the increase in volume when the silicon oxide is formed. The value of range  $R_{\rm p}$  for  $V_0$  can be estimated using simulation packages like TRIM. Also,

$$D_0 = \frac{4.4 \times 10^{22} \cdot t_{\text{BOX}}}{\text{c}} \text{ ions cm}^{-2}$$

(2)

where  $4.4 \times 10^{22} \, \mathrm{cm}^{-3}$  is the number density of silicon dioxide, c is the number of oxygen atom in the ion being implanted and  $t_{\mathrm{BOX}}$  is given in centimeter. Thus the silicon overlayer thickness and buried oxide thickness that are desired for the SOI structure determine the choice of  $V_0$  and  $D_0$ .

#### IV. PHASE SPACE OF SPIMOX IMPLANTATION

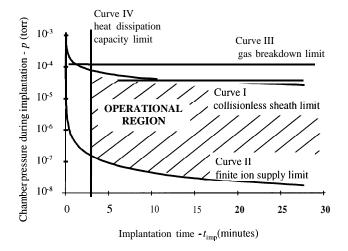

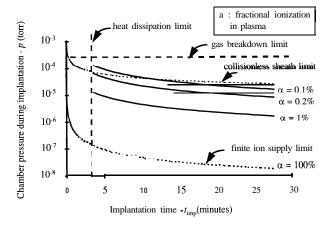

The final dimensions of the SOI structure desired fixes the implantation voltage( $V_0$ ) and the dose( $D_0$ ) by (1) and (2). The phase space is developed for a fixed  $V_0$  and  $D_0$ . Four constraints have been identified in SPIMOX implantation. Each of them is plotted in Fig. 3 on the  $t_{\rm imp}$ -p phase-space. The phase-space corresponds to the implanter used in Berkeley, for  $V_0$  of 100 kV and  $D_0$  of 2.2 x10° cm<sup>-2</sup> ( $t_{\rm Si}$  = 88 nm and  $t_{\rm BOX}$  = 100 nm). The oxygen plasma considered is dominated by  $O_2$  ion species.

The four constraints identified in this phase space are discussed below .

#### A. Collisionless sheuth

In order to obtain a mono-energetic implantation, it is important to obtain a collisionless sheath. This requires the mean-free path of the ion in the sheath to be larger than the sheath width. Modeling the dc collisionless sheath as in [6] and expressing the mean free path in terms of the chamber pressure, this requirement can be expressed in the  $t_{\rm imp}$ -p phase space by

$$p < \frac{kT}{\sigma} \cdot \frac{a}{\left(\frac{4}{9} \varepsilon_0 \left(\frac{2q}{M}\right)^{1/2}\right)^{1/2} \cdot V_o^{3/4}} \cdot \frac{1}{t_{\text{imp}}^{1/2}}$$

(3)

Fig. 3. Operational phase-space for the Berkeley implanter. The implantation voltage is 100~kV and ion dose is  $2.2~x~10^{17} cm^{-2}$ .

where k is the Boatsman's constant, T is the absolute temperature of the ions and neutrals in the plasma,  $\sigma$  is the total ion-neutral collisional and charge exchange cross-section in the sheath,  $\varepsilon_0$  is the permittivity of free space, q is the electronic charge and A4 is the mass of the ion. This constraint is shown as curve I in Fig. 3. The allowed region lies below this curve in the phase-space. Choosing a conservative value for the ion-neutral interaction (charge exchange and collisions) cross-section of 1  $0^{-14}$  cm<sup>2</sup>[7], an  $O_2^+$  dominant plasma and implantation time of 10 minutes, the pressure of operation according to this condition must be below  $7x10^{-5}$  torr.

#### B. Finite ion supply

The maximum ion current during implantation is limited by the number of ion species available in the plasma. The ion density  $(n_i)$  is dependent on the gas pressure and the fractional ionization (a) of the plasma. Assuming an ideal situation of  $\alpha=1$ , i.e., full ionization, the allowed region in  $t_{\rm imp}$ -p phasespace is

$$p \ge \frac{kTD_{\rm o}}{u_{\rm B}} \cdot \frac{1}{t_{\rm imp}} \tag{4}$$

where  $u_{\rm B}$  is the Bohm velocity for the implanted ion in the plasma given by

$$u_{\rm B} = \sqrt{\frac{q T_{\rm e}}{M}} \tag{5}$$

Here,  $T_e$  is the electron temperature in the plasma expressed in volts This constraint is shown as curve II in Fig. 3. The allowed region of operation lies above this curve. For an

electron temperature  $T_e = 2$  volt, the pressure of operation during implantation must be above 4 xl  $0^{-8}$  torr for  $t_{imp} = 10$  minutes.

# C. Gas Breakdown Voltage

The implantation voltage for an implantation process must be lower than the gas breakdown voltage for the system. The breakdown voltage and pressure for a system follows the Paschen curve [8]. This curve has to be determined for each system. On the  $t_{\rm imp}$ -p phase space, this constraint can be expressed as

$$P < p(V_0) \tag{6}$$

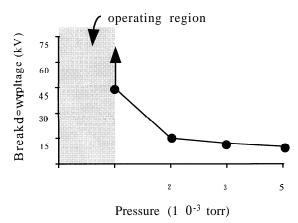

Here  $p(V_0)$  is determined from the measured Paschen curve. The breakdown measurements taken in the Berkeley PIII system is shown in Fig. 4. It is seen that for pressures below 10" torr, the breakdown voltage is well above 70 kV. The constraint is shown as curve III in Fig. 3.

Fig. 4. Breakdown voltage measurements of oxygen gas with the Berkeley reactor geometry.

### D. Heat Dissipation Capability

During implantation, the wafer temperature is to be maintained at 600 °C in order to retain the crystallinity of the over layer In steady state the implantation process should not introduce more energy in the wafer than can be dissipated by the wafer holder at that temperature. If the maximum heat dissipation capacity per unit area in the wafer is H, the time taken for implantation  $t_{\rm imp}$  is limited by the (7).

$$t_{\rm imp} \ge \frac{V_0. D_0. q}{H} \tag{7}$$

Equation (7) is represented as curve IV in Fig. 3. For commercial systems, the maximum rate of heat dissipation is typically around 30 mW °C<sup>-1</sup>cm<sup>-2</sup> by gas-conduction cooling [9] and around 1W cm<sup>-2</sup> by radiation at 600°C [PO]. For such

a cooling system, the minimum time taken to implant is 3.2 minutes for a dose of  $2.2 \times 10^{17}$  cm<sup>-2</sup> and voltage of 100 kV.

## IV. Discussion

The phase space developed for SPIMOX implantation shows that it is possible to obtain short implantation times for the high dose of oxygen for SOI fabrication. The actual operation point in the phase space depends on the fractional ionization in the plasma. The operation points corresponding to fractional ionization of **0.** 1%, 0.2% and 1% are show in Fig. 5. The phase space is plotted corresponding to  $t_{\rm BOX}$  = 100 nm and  $t_{\rm Si}$  = 88 nm ( $V_0$ =100 kV and  $D_0$ =2.2x10<sup>17</sup> cm<sup>-2</sup> for an  $O_2$ <sup>+</sup> dominant plasma).

For the lower fractional ionization of 0.1%, the minimum implantation time limited by the collisionless sheath requirement is 12 minutes. In the phase space being considered and a wafer holder heat dissipation capacity of 18 W cm<sup>-2</sup>, the minimum implantation time for an ionization fraction of 0.2% is 3.24 minutes, dictated by the heat dissipation capacity of the wafer holder. This remains true for any ionization fraction above 0.2% up to the ideal 100%. The collisionless sheath constraint boundary shown here corresponds to the sheath width being equal to the ion mean free path. For monoenergetic implantation, it is preferable to operate as far below this curve as is practical. From this consideration, it is better to have as high a fractional ionization as is permissible by the plasma source and the ion confinement technology. High ionization sources [11] like electron cyclotron resonance (ECR), transformer couple plasma (TCP) and helical sources are available which can give high fractional ionization up to 1-10% as is required for the SPIMOX implantation.

Fig. 5. The locus of operation points on phase space for fractional ionization of 0.1%, 0.2% and 1% in the plasma. The phase space is plotted for implantation voltage of  $100\,\mathrm{kV}$  and a dose of  $2.2\times10^{17}\,\mathrm{cm}^{-2}$ .

The minimum implantation time is limited by the heat dissipation constraint for SPIMOX. For higher implantation dose, required for thicker buried oxide layers, and for higher implantation voltage, required for thicker top silicon overlayer, this limiting constraint becomes more severe as seen from (7). The breakdown voltage constraint also becomes significant for high voltage implants. However, with the move towards thinner dimensions for SOI, due to fabrication as well as device performance considerations [12], these factors are not limitations for SPIMOX application.

# V. Conclusion

Higher throughput and simpler implanter are the main advantages of SPIMOX over the conventional SIMOX. The operational region of SPIMOX implantation is plotted on a phase space of the time taken for implantation and the chamber-pressure during implantation. High ionization plasma sources are required to have the maximum advantage of throughput in SPIMOX. The throughput of implant is limited by the heat dissipation capacity of the wafer holder. Using high density plasma sources, high throughput independent of the wafer size can be achieved for thin SOI fabrication using SPIMOX.

#### REFERENCE

- D.A. Antoniadis, "SOI CMOS Front-End Technology: Options and Tradeoffs", "1995 IEEE International SOI Conference, pp. I-3.

- [2] S. Cristoloveanu and S.S. Li, Electrical Characterization of Silicon-On-Insulator Materials and Devices, Kulwer Academic Publishers, Boston, 1995, pp.10

- [3] J.B. Liu, S.S.K. Iyer, J. Min, PK. Chu, R. Gronsky, C. Hu, and N.W. Cheung, "Synthesis of Buried Oxide by Plasma Implantation with Oxygen and Water Plasma" 1995 IEEE International SOI Conference, pp. 166-167

- [4] N. W. Cheung, "Plasma immersion ion implantation for ULSI", Nuclear Instruments Methods, vol. B55, pp.81 1-820, 1991.

- [5] J.B. Liu, S.S.K. Iyer, J. Min, P. Chu, R. Gronsky, C. Hu and N. Cheung, "Formation of buried oxide in silicon using separation by plasma implantation of oxygen" *Applied Physics Letters*, vol. 67-1 6, 1995, pp. 2361-2363.

- [6] M.A. Lieberman and A.J. Lichtenberg, Principles of Plasma Discharges and Materials Processing, John Wiley, New York, 1994, pp. 164-1 66.

- [7] E.A. Mason and E.W. McDaniel, Transport Properties of Ions in Gases, John Wiley & Sons, Inc., 1988.

- [8] M.A. Lieberman and A.J. Lichtenberg, Principles of Plasma Discharges and Materials Processing, John Wiley, New York, 1994, pp.457-460.

- [9] M.E. Mack, "Wafer Cooling and Wafer Charging", Handbook of Ion Implantation Technology, J.F. Zeigler, Ed. North-Holland, Amsterdam, 1992, pp. 616.

- [10] T. C. Smith, "Wafer Cooling and Photoresist Masking Problems in Ion Implantation", *Ion Implantation: Equipment and Techniques*, H. Ryssel and H. Glawischnig, Eds. Springer-Verlag, New York, 1983, pp. 199

- [11] M.A. Lieberman and A.J. Lichtenberg, Principles of Plasma Discharges and Materials Processing, John Wiley, New York, 1994, pp. 16.

- [12] M. Alles, W. Krull and L. Allen, "Implications of thin buried-oxide for SIMOX circuit performance", *Silicon-on-Insulator Technology and Devices, S.* Cristoloveanu, Ed., The Electrochemical Society, Inc., New Jersy, 1994, pp. 459-464.