# **Three-Pole Analysis Model to Predict SI and EMC Effects**

# A. Ege Engin<sup>1</sup>, Mart Coenen<sup>2</sup>, Heiko Koehne<sup>1</sup>, Grit Sommer<sup>1</sup>, Werner John<sup>1</sup>

<sup>1</sup>Fraunhofer Institute for Reliability and Microintegration, Dept. Advanced System Engineering Gustav-Meyer-Allee 25 D-13355 Berlin

E-mail: <u>Ege.Engin@izm.fraunhofer.de</u>, <u>Grit.Sommer@izm.fraunhofer.de</u>, <u>Heiko.Koehne@izm.fraunhofer.de</u>, <u>Werner.John@pb.izm.fraunhofer.de</u>

<sup>2</sup> Philips Semiconductors, Systems Laboratories Eindhoven (SLE)

E-mail: Mart.Coenen@Philips.com

**Abstract** - Accurate driver and package models are necessary to analyze the signal integrity (SI) and electromagnetic compatibility (EMC) issues on digital circuits. 2-pole models that assume an ideal power distribution system (PDS) are commonly used in modeling the SI of signal lines. This assumption makes real SI and EMC analysis worthless or at least only useful under certain restrictions. In order to account for all current return paths, the power and ground lines have to be considered as well. As such, the driver and the package is modeled as a 3-pole and a 6-pole network, respectively.

### 1. INTRODUCTION

Over the years, 2-pole models have been used in various SI and EMC analysis of digital circuits. These models assume infinite decoupling or an ideal PDS, such that the power line can be regarded as an AC ground. This assumption allows the treatment of the Input/Output (I/O) drivers as 2-pole networks and the signal interconnect between the transmitter and receiver as a 2-port network (e.g., as a single transmission line) referenced to the AC short circuited power and/or ground. To account for the power supply noise, a model is necessary which includes the parasitics on the PDS. In this work, such models are called 3-pole models. Particularly, the associated driver and package models will be called 3-pole driver models and 6-pole package models.

IBIS is the most commonly used 2-pole I/O driver model, which provides the I/O device characteristics through V/I data. A 2-pole driver model assumes an ideal PDS. However, the output waveform of a CMOS circuit is mainly determined by the relation of its input voltage to the power and ground rails. The rail-to-rail switching behavior also emphasizes the importance of including the effect of power supply voltage fluctuations in the driver model. Inversely, with a 3-pole driver model the noise on the power rails due to switching drivers can be examined as well [1]. Using a 2-pole model is obvious for simplicity sake but makes real SI and EMC analysis worthless or at least only useful under certain restrictions.

In order to capture the power supply noise and the correct behavior of the return currents, a package model that incorporates the signal, power, and ground lines is necessary as well. Also, the transition-dependent switching behavior can be observed with such a model.

With this in mind, an IC package evaluation project was started in the framework of MEDEA+ Project MESDIE [2], where it turned out that using the entire circuitry is too complex for any analogue device simulator and using the IBIS models is too simplified for EMC as the signal return current paths are not taken into account properly.

Further analysis has shown that IC package optimization is determined by:

- the measures taken at the silicon die,

- the I/O and supply bond pad allocation,

- the on- or off-chip decoupling (with core and I/O),

- the IC package layer allocation,

- the BGA ball allocation and the PCB layer application with the used decoupling.

## 2. 3-POLE MODEL

In order to analyze the signal transmission in digital circuits, power and ground must be included in addition to the signal line in the interconnect model.

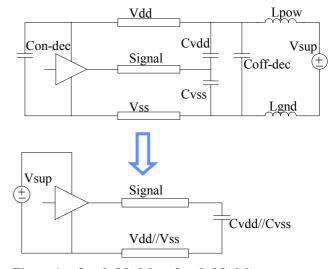

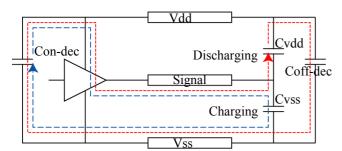

Figure 1 3-pole Model vs. 2-pole Model

On top of Figure 1, a 3-pole model can be seen. The load is represented by capacitors (Cvdd, Cvss) to power (Vdd) and ground (Vss), and the power supply is on the right side of the figure represented by a voltage source (Vsup) and parasitic inductances (Lpow, Lgnd). An arbitrary model is assumed to be available for the interconnect between the driver and the load. If the on-chip and offchip decoupling capacitors on the driver and load side (Con-dec, Coff-dec) provide infinite decoupling, the power line can be seen as an AC ground. Under this assumption, an equivalent 2-pole model can be obtained by parallel connecting the power and ground lines as shown at the bottom of Figure 1. With SI simulations the interconnect network will be reduced even further to asymmetric  $\pi$ - or T-networks. The 2-pole model is not applicable, if there is insufficient decoupling, or if there are many drivers switching simultaneously, such that the PDS cannot be regarded as ideal [3].

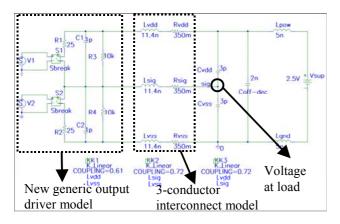

By means of a simple 3-pole output driver circuit, able to be simulated in SPICE, a three-pole model has been created, see Figure 2.

Figure 2 Three-pole model for SI and EMC analysis

The transistors forming the CMOS driver circuit are modelled by resistors (R1, R2) representing the onresistance of the devices and by voltage controlled switches (S1, S2) with smooth characteristics. The period and the fall and rise times of the inner circuitry driving the CMOS is applied in the simulation through independent voltage sources (V1, V2) connected to these switches. The parasitic capacitance associated with the driver, mainly due to the protection diodes, is represented by two capacitors (C1, C2). Some parallel-connected resistors (R3, R4) with negligible admittance may represent leakage or DC currents and allow that SPICE can make a DC bias point analysis.

The power, signal, and ground lines are represented by inductors (Lvdd, Lsig, Lvss) with mutual coupling coefficients (K1, K2, K3), and resistors (Rvdd, Rsig, Rvss). The interconnects modelled here consist of 3 identical coplanar traces in parallel. The distances between

the left (Vdd) and middle (Signal), and the middle and right (Vss) traces are equal, and the length of each trace is 1cm. Such a configuration could be found by packages without any power or ground planes. The partial inductance and resistance matrices were calculated at the frequency of the first harmonic of the input signal by using a tool based on the partial equivalent electric circuit (PEEC) method [4]. Such models for the parasitic elements of chip packages are commonly used to simulate simultaneous switching noise (SSN), by including several drivers using the same PDS [5].

The power supply network up to the package is represented by a voltage source (Vsup) and parasitic inductances (Lpow, Lgnd), which are decoupled in the model through an ideal capacitor (Coff-dec). Finally, two capacitors to power (Cvdd) and ground (Cvss) represent the system load.

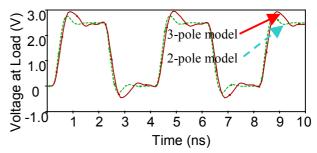

# Motivation: Comparing the 2-pole and 3-pole models

A comparison between the 2-pole and 3-pole models can be made by using the fact that a 2-pole model assumes an ideal PDS. Therefore, a 2-pole model can be obtained by connecting an ideal decoupling capacitor or an ideal voltage source between the power and ground poles of the driver in the 3-pole model. Figure 3 shows the voltage to ground on the load (i.e., voltage drop on Cvss) for the circuit in Figure 2. Obviously, the 2-pole model gives an optimistic result. In case of SSTL 2 interface standard [6], for example, the 2-pole model would not forecast the excessive overshoot of the input voltage on the receiver, which should not exceed 2.8V.

Figure 3 Comparison of the two-pole and three-pole models

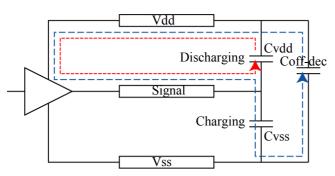

The discrepancy between the results can be explained by examining the current loops. Figure 4 shows the main current loops for a low-to-high transition. The CMOS driver pulls the output to Vdd. The load capacitance to power (Cvdd) discharges while the load capacitance to ground (Cvss) charges through the off-chip decoupling capacitor. It can be seen that the signal current returns mainly through the power line. Similarly, the return current would flow through the ground line for a high-to-low transition. As stated earlier, the 2-pole model implies infinite decoupling, so that an ideal decoupling capacitor is assumed to be connected between the power and ground

poles of the driver as in <u>Figure 5</u>. As such, for example the Lvss and Lvdd inductances in <u>Figure 2</u> would be connected in parallel, which is not realistic.

Figure 4 Actual current loops for a high-to-low transition

An on-chip decoupling capacitor would provide additional current loops to the existing ones in <u>Figure 4</u>. In <u>Figure 5</u>, it can be seen that for these current loops, the return currents flow mainly through the ground line. By superimposing the current loops in <u>Figure 4</u> and <u>Figure 5</u>, the power and ground lines can be regarded as effectively short-circuited, so that the interconnects could be represented by a simplified 2-pole model as in Figure 1.

Figure 5 Additional (nonexistent) current loops for a high-to-low transition implied by the 2-pole model

If there is insufficient on-chip decoupling as in the example of Figure 2, the 2-pole model implies nonexistent current return paths. Therefore, the 2-pole model is not applicable in such a case as it can be seen in Figure 3. Furthermore, regardless of the availability of the on-chip decoupling, the package should be modeled as a 6-pole network to capture the correct current return paths, especially in case of unsymmetrical signal-power and signal-ground loops and to be able to calculate the ground bounce between the IC's substrate and the PCB's Vsslayer.

## 3. DISTRIBUTED 6-POLE PACKAGE MODEL

Lumped package models as in <u>Figure 2</u> are only adequate up to certain frequencies. Also, the parasitic elements of the separate segments of the interconnect (e.g., wirebonds, package traces, etc.) are not distinguishable from each

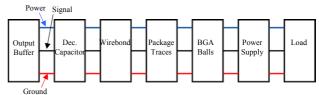

other. On the other hand, distributed 2-port package models assume an ideal PDS. To overcome these limitations a new distributed 6-pole package model is proposed as shown in <u>Figure 6</u>.

Figure 6 New Distributed 6-Pole Package Model

The three lines between the blocks in Figure 6 represent the power, signal, and ground connections, such that each block can be seen as a 6-pole, considering the output and input. By defining a (virtual) global reference point, the voltage drop along the conductors can be modeled, which is important for EMC considerations. Alternatively, by assigning one of the conductors in the package interconnect as the reference, the package can be seen as a 4-port network. In this case, the considered voltages are always locally referenced, which is suited for SI investigations.

Assuming that there is no electromagnetic coupling between the blocks (i.e., the only coupling is at the ports), each block can be characterized separately. Depending on the design of the package, various blocks can be moved, deleted, or added, such that the influence of each interconnect segment on the signal quality can be easily determined. Also, distributed models can be used for electrically long interconnects with uniform cross sections (e.g., package traces), incorporating power and ground plane models [7].

To capture the nonlinear behavior of the drivers, which can be represented by behavioral or transistor-level models [8], the circuit simulation must be done in the time domain. The equivalent electrical models of the blocks that represent a segment of the interconnect can be extracted through field simulation, measurement, or analytical methods. If the total package can be represented by cascaded blocks as in Figure 6, the chain matrix formulation can be applied as an alternative. By multiplying the chain matrices of the blocks, the total interconnect could be represented by a single chain matrix. The implementation of such network matrices in SPICE to make simulations in the time domain is inconvenient, but possible.

The model in <u>Figure 6</u> assumes that there is negligible coupling to neighboring signal lines. It can easily be extended to include the coupling between the signal lines, by including these lines in the models of the blocks and in port definitions. In case of differential signaling, for example, the total interconnect could be represented by an 8-pole network. By including neighboring signal lines in the model, crosstalk or SSN investigations can be made.

#### 4. CASE STUDY

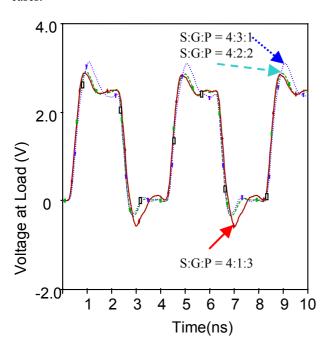

3-pole driver model together with the distributed 6-pole package model were used to investigate the assignment of supply wirebonds in a BGA package with no on-chip decoupling. The package traces were modeled as transmission lines including the power and ground planes [9], and the BGA balls were modeled through optimization of a compact electrical model by matching the full-wave simulation of the structure. The number of the total supply wirebonds was kept constant and equal to the number of signal wirebonds (i.e., S:(G+P)=1:1). The assignment of the supply wirebonds to power and ground was varied and three cases were investigated:

- 1. ...GSGSGSPS... (i.e., S:G:P = 4:3:1)

- 2. ...PSPSPSGS... (i.e., S:G:P = 4:1:3)

- 3. ...GSPSGSPS... (i.e., S:G:P = 4:2:2)

<u>Figure 7</u> shows the voltage to ground at the load for these cases.

Figure 7 Influence of the assignment of supply wirebonds

As expected from the switching behavior of the CMOS driver in Figure 4, during a low-to-high transition, the signal return current flows mainly through the power line. In this case having low impedance for the signal-power loop (e.g., by providing more power wirebonds) improves the signal quality. Inversely, for a high-to-low transition, mainly the parasitics of the signal-ground loop affects the signal quality. From Figure 7, it can be seen that an optimum voltage behavior is achieved if the supply wirebonds are evenly distributed between power and ground. Even assignment provides the minimum

inductance for the supply loop, and an optimum inductance for the signal-power and signal-ground loops.

### 5. CONCLUSION

With this new model, all kind of artifacts in either the circuit topology or the geometrical design can be analyzed correctly. By means of changing some lumped element values with the model, the output driver impedance can be modeled for both status transitions. Crowbar current can be taken into account with the 3-pole driver model as well. Power supply perturbations due to package parasitics, and its influence on signal quality can be modeled by a distributed 6-pole package model which is introduced in this paper. This model is applicable over a broader frequency range than the existing models.

As can be seen from the list of items which do influence package design, the output structure modeling is a dominant factor that thereafter allows a new way of approaching "old" problems. Simultaneously switching drivers with fast edge rates compels the consideration of non-ideal PDS due to the chip package parasitics.

### 6. REFERENCES

- [1] Kaladhar Radhakrishnan, Yuan-Liang Li, and William P. Pinello, "Integrated Modeling Methodology for Core and I/O Power Delivery", 51st Electronic Components and Technology Conference, pages 1107–10, 2001.

- [2] http://www.mesdie.org/

- [3] Brian Young, <u>Digital Signal Integrity: Modeling and Simulation with Interconnects and Packages</u>, Prentice Hall (2001), Chapters 1,2.

- [4] Mattan Kamon, Michael J. Tsuk, and Jacob K. White, "FASTHENRY: A Multipole-Accelerated 3-D Inductance Extraction Program", IEEE Transactions on Microwave Theory and Techniques, vol.42, no.9, pages 1750-8, Sep. 1994.

- [5] Ron K. Poon, <u>Computer Circuits Electrical Design</u>, Prentice Hall (1995), Chapter 8

- [6] Stub Series Terminated Logic for 2.5 V (SSTL\_2), JESD8-9B, JEDEC Standard

- [7] Sungjun Chun, Larry Smith, Ray Anderson and Madhavan Swaminathan, "Model to Hardware Correlation for Power Distribution Induced I/O Noise in a Functioning Computer System", Electronic Components and Technology Conference (ECTC), pages 319-24, May 2002.

- [8] S. Hall, G. Hall and J. McCall, <u>High-Speed Digital System Design: A Handbook of Interconnect Theory and Design Practices</u>, John Wiley and Sons (2000), Chapter 7.

- [9] Larry Smith., "Simultaneous Switch Noise and Power Plane Bounce for CMOS Technology", Proceedings of IEEE 8th Topical Meeting on Electrical Performance of Electronic Packaging, pages 163–5, Oct. 1999.