## Electrical observations of filamentary conductions for the resistive memory switching in NiO films

D. C. Kim,<sup>a),b)</sup> S. Seo, S. E. Ahn, D.-S. Suh, M. J. Lee, B.-H. Park, and I. K. Yoo *Samsung Advanced Institute of Technology, Suwon 440-600, Korea*

I. G. Baek,<sup>a),c)</sup> H.-J. Kim, E. K. Yim, J. E. Lee, S. O. Park, H. S. Kim, U-In Chung, J. T. Moon, and B. I. Ryu

Process Development Team, Semiconductor R & D Center, Samsung Electronics, Co. Ltd., San #24, Nongseo-Ri, Kiheung-Eup, Yongin-City, Kyeonggi-Do 449-711, Korea

(Received 10 November 2005; accepted 3 April 2006; published online 15 May 2006)

Experimental results on the bistable resistive memory switching in submicron sized NiO memory cells are presented. By using a current-bias method, intermediate resistance states and anomalous resistance fluctuations between resistance states are observed during the resistive transition from high resistance state to low resistance state. They are interpreted to be associated with filamentary conducting paths with their formation and rupture for the memory switching origin in NiO. The experimental results are discussed on the basis of filamentary conductions in consideration of local Joule heating effect. © 2006 American Institute of Physics. [DOI: 10.1063/1.2204649]

Recently the electric-field controlled resistive memory switching phenomenon in metal oxides with metal-metal oxide-metal (M-O-M) structure has drawn much attention due to its possibility for nonvolatile memory applications. Despite of its early discovery in the 1960s the microscopic physical origins of the resistive memory switching are still not clearly understood.<sup>1</sup> To explain the memory switching in oxide materials including binary oxides and perovskite oxides, various models have been proposed such as filamentary conductions, charge trapping defects states inside the band gap, trap-controlled space-charge-limited current, and charge trap states at metal/oxide interfaces with a change of a Schottky-like barrier.<sup>1–3</sup> However, further experimental and theoretical investigations are required to understand the resistive memory switching mechanism in metal oxides. In this letter, we report the memory switching *I-V* curves using the current-bias method in submicron sized NiO memory cells, which suggest percolative formation and rupture of filamentary conducting paths for the memory switching origin in NiO. The memory switching origin in NiO seems to be associated with local, filamentary conduction with nonnegligible Joule heating effect.

Details on NiO film depositions and measurement setup are described elsewhere.<sup>2,3</sup> For fabrications of memory cells with submicron size of area, 0.18  $\mu$ m complementary metal-oxide semiconductor (CMOS) technologies have been used.<sup>4</sup> The sizes of cell area measured by the scanning electron microscopy are 0.05, 0.56, and 9.4  $\mu$ m<sup>2</sup>, respectively.

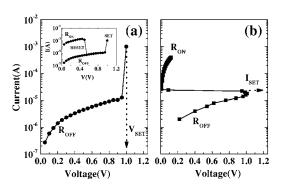

After the forming process on the pristine memory cell, the reversible bistable resistive memory switching is generally observed by a voltage sweep.<sup>2</sup> As the applied voltage increases, the resistive transition from a stable low resistance  $R_{ON}$  state to a stable high resistance  $R_{OFF}$  state, the RESET, appears at ~0.5 V. At the  $R_{OFF}$  state, the resistive transition from  $R_{OFF}$  state to  $R_{ON}$  state, the SET, occurs by increasing the voltage up to ~1 V [see the inset of Fig. 1(a)]. For the SET and the forming process, an appropriate current compliance should be imposed for the memory switching. Experimentally this means that the current is limited by an external circuit, and the voltage sweep stops when the measured current reaches a current compliance value.<sup>2–4</sup> The voltage required for each transition is defined as the RESET voltage ( $V_{RESET}$ ) and the SET voltage ( $V_{SET}$ ). As shown in Fig. 1(a) the voltage-biased SET inevitably results in a sudden jump of the measured current at  $V_{SET}$ . This blurs the exact role of the external current at the SET transition point. In contrast, if the SET is driven by the current bias, one can reveal the real *I-V* data from the maximum current value at  $R_{OFF}$  state to the current compliance value at  $R_{ON}$  state during the SET, unobservable in voltage-biased SET cases [Fig. 1(b)].

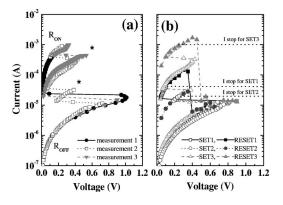

Figure 2(a) shows the SET *I-V* curves using the currentbias method. The measurement current is swept from 0 to 1 mA, a typical current compliance value for the voltage-biased SET cases. At low and high current ( $I < 10 \ \mu A$ ,  $I > 500 \ \mu A$ ) regions, resistance values from different measurements are identical with formation of stable  $R_{\rm ON}$  and  $R_{\rm OFF}$  states. However, at an intermediate current region ( $10 \ \mu A < I < 500 \ \mu A$ ), the intermediate resistance states could be observed. It is found that the intermediate

FIG. 1. (a) Voltage-biased SET *I-V* curve of memory switching with a current compliance of 1 mA. The inset shows the memory switching *I-V* curves by voltage-biased SET and RESET. (b) Current-biased SET *I-V* curve of memory switching.  $I_{\text{SET}}$  is a threshold current required for transition to the stable  $R_{\text{ON}}$  state. All data are obtained from a 0.05  $\mu$ m<sup>2</sup> sized cell.

88, 202102-1

Downloaded 03 May 2011 to 129.234.252.65. Redistribution subject to AIP license or copyright; see http://apl.aip.org/about/rights\_and\_permissions

<sup>&</sup>lt;sup>a)</sup>Authors to whom the correspondence should be addressed.

<sup>&</sup>lt;sup>b)</sup>Electronic mail: dongchirl.kim@samsung.com

<sup>&</sup>lt;sup>c)</sup>Electronic mail: ig.baek@samsung.com

<sup>© 2006</sup> American Institute of Physics

FIG. 2. (a) Current-biased SET *I-V* curves measured in a 0.05  $\mu$ m<sup>2</sup> sized cell. The asterisks denote the intermediate resistance states between  $R_{OFF}$  and  $R_{ON}$  states. (b) Memory switching *I-V* curves with current-biased SET (unfilled data) and voltage-biased RESET (filled data). For SET1, the current sweep is stopped at *I*=40  $\mu$ A and the voltage is swept for the RESET. For SET2 and SET3, the stop currents are 20  $\mu$ A and 1 mA, respectively. Each stop current is denoted by a dotted line with index.

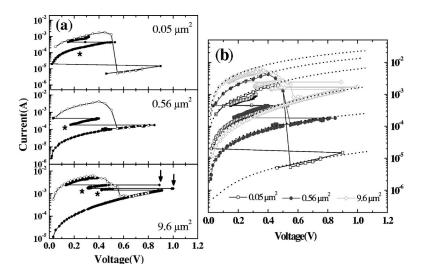

resistance states are not necessarily observed in every SET case. These occur in random with different numbers of intermediate resistance states. As shown in Fig. 2(a), single resistive transition from  $R_{\text{OFF}}$  to  $R_{\text{ON}}$  could be observed in some cases (measurement 1), whereas multiple intermediate resistance states with successive resistive transitions could be observed in other cases (measurements 2 and 3). The observed intermediate resistance states phenomenon looks quite similar to the "snapback" behavior in ultrathin SiO<sub>2</sub> films.<sup>5</sup> Compared to this, the differences should be noted that our NiO film has a thickness of 20 nm, and each intermediate resistance state has its own memory switching. The estimated electric field at  $V = V_{\text{SET}}$  (~1 V) is about 0.5 MV/cm. This value is lower than the electric field normally required for the breakdown of oxide films (i.e., the order of several MV/ cm). However, it should be mentioned that the electric field for the forming process which initiates the memory switching is larger than 1 MV/cm. In our case the forming voltage is usually above  $\sim 3$  V corresponding to 1.5 MV/cm. If the current sweep is stopped at a certain intermediate resistance state and the voltage is swept from zero, the resistance switches back to  $R_{\text{OFF}}$  at  $V \sim V_{\text{RESET}}$  [see Fig. 2(b)]. Figure 3 shows the memory switching I-V curves in different cell sizes. The intermediate resistance states can be observed irrespective of the cell size. Experimentally, the intermediate resistance states disappear above a certain critical current ( $I_{\text{SET}}$ ), which can be regarded as a threshold current required to have a reproducible  $R_{\text{ON}}$  state stabilized on the same RE-SET *I-V* curve. From repeated memory switchings the maximum value of  $I_{\text{SET}}$  is found to have a weak dependence on cell size: 0.5, 1, and 4 mA for 0.05, 0.56, and 9.4  $\mu$ m<sup>2</sup>, respectively.

The observed phenomena give important clues on the memory switching origin in NiO films. The SET I-V curves which are shown to be a current-controlled negative differential resistance case suggest a percolative formation of localized filamentary conducting paths.<sup>1,5</sup> The intermediate resistance states can be explained in terms of formation of additional percolation paths during the current stress. Similar to Fig. 2(b), overlaps of resistances can be observed by plotting the memory switching I-V curves of different cells together [Fig. 3(b)]. This again suggests the filamentary conductions where a number of filamentary conducting paths locally generated would give the resistance of the memory cell. The resistance overlap indicates that filamentary paths would not be formed totally at random. Rather there would be some preference for forming certain filamentary paths during the current stress, resulting in similar resistances. Irrespective of its detailed mechanism, the RESET of the memory switching could be attributed to a rupture of these localized conducting paths. These support the filamentary conduction model in NiO memory cell, where the memory switching could be originated from percolative formation and rupture of localized filamentary conducting paths.<sup>1</sup> It is interesting to see what would happen in case of the RESET using the current-bias method. If an unstable low resistance state is reached by the SET with a low current compliance value (for example,  $<50 \ \mu A$  in 0.05  $\mu m^2$  sized cells), one might observe transitions between intermediate resistance states or anomalous resistance fluctuations during the current sweep, as shown in Figs. 2 and 3. The details of anomalous resistance fluctuations will be discussed later. If the current compliance value at the SET is high enough (for example, >1 mA in 0.05  $\mu$ m<sup>2</sup> sized cells) and a stable low resistance  $R_{\rm ON}$  state is obtained, the resistance becomes noisy as the measured voltage becomes close to  $V_{\text{RESET}}$ . At  $V \ge V_{\text{RESET}}$ , resistance decreases suddenly and does not switch back to  $R_{\text{OFF}}$ . This indicates that stable filamentary conducting paths can be ruptured (=RESET) only by the voltage sweep. Imposing higher current would make conducting paths perma-

FIG. 3. (Color online) (a) Cell size dependence of memory switching *I*-*V* curves at room temperature. The filled data are the current-biased SET curves whereas the unfilled data are the voltage-biased RESET curves. The asterisks denote the intermediate resistance states, and the arrows denote the anomalous resistance fluctuations. (b) Memory switching *I*-*V* curves plotted together. The dotted lines are guides for the eyes.

Downloaded 03 May 2011 to 129.234.252.65. Redistribution subject to AIP license or copyright; see http://apl.aip.org/about/rights\_and\_permissions

nent with an absence of memory switching properties. This could be understood in the similar context of the irreversible breakdown of oxide films. If the current compliance value is too high (for example, >10 mA in 0.05  $\mu$ m<sup>2</sup> sized cells) at the SET or the forming process, it would result in a permanent low resistance state by the irreversible breakdown.

During the current-biased SET, anomalous resistance fluctuations between intermediate resistance states and  $R_{OFF}$ state are also observed as denoted by arrows in the bottom figure of Fig. 3(a). The cell resistance randomly fluctuates between R<sub>OFF</sub> state and intermediate resistance states until finally stabilized on  $R_{ON}$  state. The anomalous resistance fluctuations also appear in similar manners to those of intermediate resistance states. From repeated switchings it is observed that the occurrence increases as the cell size increases. It is dominantly observed in the largest cell, which has the lowest  $R_{OFF}$ . This can be related to the average power dissipated at the SET and RESET processes. The estimated SET (RESET) powers by multiplying maximum I and V values at  $R_{\text{OFF}}$  ( $R_{\text{ON}}$ ) state are 0.014 (0.81), 0.68 (1.68), and 1.27 (2.24) mW for 0.05, 0.56, and 9.4  $\mu$ m<sup>2</sup> sized cells, respectively. The anomalous resistance fluctuations appear dominantly when the SET power becomes comparable to the RE-SET power. From the view of the filamentary conduction model, these can be interpreted to be from successive formation and rupture of filamentary conducting paths. Due to the high power at the SET comparable to that of the RESET, the resistance changed by the SET process successively suffers the RESET process and returns back to  $R_{\text{OFF}}$  state again. This implies a certain role of the Joule heating effect on the memory switching.

The Joule heating effect by the external current is considered for the formation and rupture of conducting filaments. For the rupture of filaments (RESET), one can roughly estimate the temperature of formed filaments using the steady state temperature model, where the equation is given by  $T_m = (T_o^4 + J^2 \rho r/2P_w)^{1/4} \cdot {}^{10} T_m$  is the filament temperature raised by Joule heating,  $T_o$  is the room temperature (=300 K), J is the current density,  $\rho$  is the sample resistivity, r is the filament radius, and  $P_w$  is the radiative loss parameter for the filament, which can be roughly assumed to be  $\sim 3$  $\times 10^{-7}$  W m<sup>-2</sup> K<sup>-4</sup>.<sup>6</sup> This equation gives the temperature over 720 K with the current of 200 nA for a Ni nanowire with r=5 nm and  $\rho_{\rm Ninanowire}$ =5×10<sup>-4</sup>  $\Omega$  cm.<sup>7</sup> Compared to the case of a Ni nanowire as an idealized filament, the formed filaments in NiO would have higher resistance with local variations. In a "nonuniform, flawed filament" model, the rupture of a filament is well considered to take place only at a high resistance flaw inside the filament by local Joule heating.<sup>8</sup> This tells us the Joule heating effect as a nonnegligible factor for the RESET. The high temperature induced by the external current at the flawed, high resistance region of the filament would contribute to the rupture of filament. Thermal enhancement of electromigrations and local field-induced oxidation effects could be significant, although the electric field effect on the RESET needs to be investigated separately.9,10

The Joule heating effect for the filament formation (SET) could also be considered. It should be noted that the current density would be over  $10^7 \text{ A/cm}^2$  for a localized filament with r=5 nm at the region where the intermediate resistance states appear. The percolative formation of the conducting filament would be initiated at  $V \approx V_{\text{SET}}$  with I  $< I_{\text{SET}}$ . The first filament may be formed in an incomplete way, and additional filaments could be successively formed nearby the first filament by local Joule heating due to a high current density.<sup>5</sup> This would result in intermediate resistance states. As the current approaches  $I_{\text{SET}}$ , the current-biased filament formations become stabilized, finally reaching the  $R_{ON}$ state.

In summary, the bistable resistive memory switching in submicron sized NiO memory cells has been measured. The intermediate resistance states between  $R_{OFF}$  and  $R_{ON}$  states and anomalous resistance fluctuations between intermediate resistance states and  $R_{\text{OFF}}$  state have been observed by using the current-bias method for the SET. The observed phenomena could be explained by formation and rupture of localized filamentary conducting paths as the memory switching origin in NiO memory cells. The Joule heating effect is considered to play an important role on the memory switching. The microscopic nature of conducting filaments and electric-field effects on the memory switching mechanism still need further investigation.

- <sup>1</sup>G. Dearnaley, A. M. Stoneham, and D. V. Morgan, Rep. Prog. Phys. 33, 1129 (1970), and references therein.

- <sup>2</sup>S. Seo, M. J. Lee, D. H. Seo, E. J. Jeoung, D.-S. Suh, Y. S. Joung, I. K. Yoo, I. R. Hwang, S. H. Kim, I. S. Byun, J.-S. Kim, J. S. Choi, and B. H. Park, Appl. Phys. Lett. 85, 5655 (2004), and references therein.

- <sup>3</sup>S. Seo, M. J. Lee, D. H. Seo, E. J. Jeoung, D.-S. Suh, Y. S. Joung, I. K. Yoo, I. R. Hwang, S. H. Kim, I. S. Byun, J.-S. Kim, J. S. Choi, and B. H. Park, Appl. Phys. Lett. 86, 093509 (2005), and references therein.

- <sup>4</sup>I. G. Baek, M. S. Lee, S. Seo, M. J. Lee, D. H. Seo, D.-S. Suh, J. C. Park,

- S. O. Park, H. S. Kim, I. K. Yoo, U-I. Chung, and J. T. Moon, Tech. Dig. Int. Electron Devices Meet. 2004, 587.

- <sup>5</sup>T. P. Chen, M. S. Tse, and X. Zeng, Appl. Phys. Lett. 78, 492 (2001).

- <sup>6</sup>M. Knobel, P. Allia, C. Gómez-Polo, H. Chiriac, and M. Vázquez, J. Phys. D 28, 2398 (1995).

- <sup>7</sup>D. N. Davydov, J. Haruyama, D. Routkevitch, B. W. Statt, D. Ellis, M. Moskovits, and J. M. Xu, Phys. Rev. B 57, 13550 (1998).

- <sup>8</sup>R. D. Gould, J. Non-Cryst. Solids 7, 236 (1972).

- <sup>9</sup>R. Fors, S. I. Khartsev, and A. M. Grishin, Phys. Rev. B 71, 045305 (2005)

- <sup>10</sup>J. H. Hsu, H. W. Lai, H. N. Lin, C. C. Chuang, and J. H. Huang, J. Vac. Sci. Technol. B 21, 2599 (2003).